Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 63

Chapter 5: Functional Description—ALTMEMPHY

5–17

Block Description

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

For Stratix IV and Stratix III devices, the PLL reconfiguration is done using the

phase-shift inputs on the PLL instead of using the PLL reconfiguration megafunction.

Table 5–4

shows the Stratix IV and Stratix III PLL clock outputs.

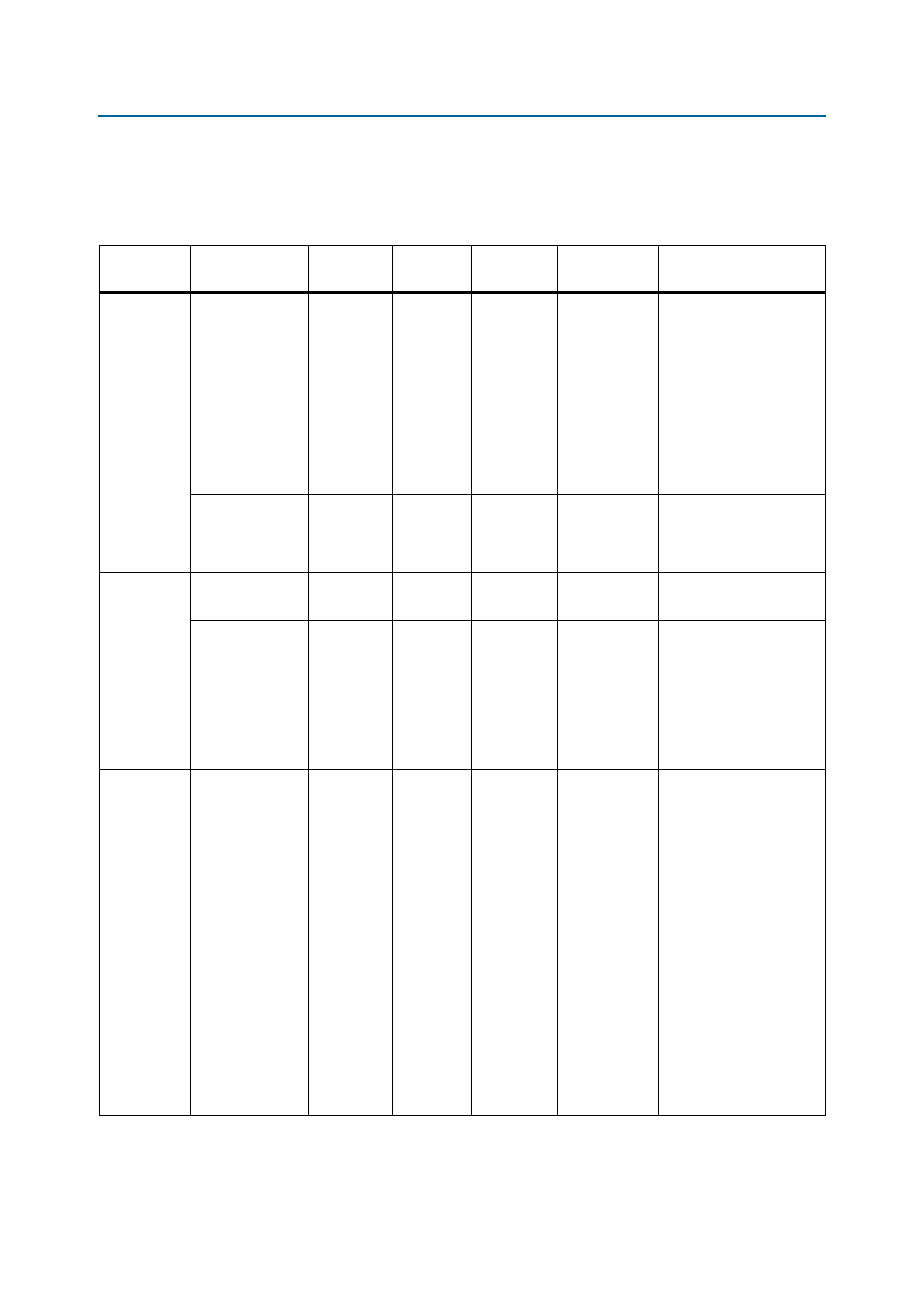

Table 5–4. DDR2 SDRAM Clocking in Stratix IV and Stratix III Devices (Part 1 of 2)

Design Rate

Clock Name

(1)

Postscale

Counter

Phase

(Degrees)

Clock Rate

Clock Network

Type

Notes

Half-rate

phy_clk_1x

and

aux_half_

rate_clk

C0

30

Half-Rate

Global

The only clock

parameterizable for the

ALTMEMPHY

megafunction. It is set to

30° to ensure proper

half-rate to full-rate

transfer for write data and

DQS. This clock also feeds

into a divider circuit to

provide the PLL scan_clk

signal for reconfiguration.

aux_full_

rate_clk

C2

60

Full-Rate

Global

The aux_clk. The

60

-offset maintains edge

alignment with the offset

on phy_clk_1x.

Full-rate

aux_half_

rate_clk

C0

0

Half-Rate

Global The

aux_clk

.

phy_clk_1x

and

aux_full_

rate_clk

C2

0

Full-Rate

Global

The only clock

parameterizable for the

ALTMEMPHY

megafunction. This clock

also feeds into a divider

circuit to provide the PLL

scan_clk

signal for

reconfiguration.

Half-rate and

full-rate

mem_clk_2x

C1

0

Full-Rate

Special

Generates mem_clk that

provides the reference

clock for the DLL. A

dedicated routing resource

exists from the PLL to the

DLL, which you select with

the regional routing

resource for the mem_clk

using the following

attribute in the HDL:

(-name global_signal

dual_regional

_clock;

-to dll~DFFIN

-name global_signal

off)

. If you use an

external DLL, apply this

attribute similarly to the

external DLL.