Read datapath, Read datapath –20, This topic describes the read datapath – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 66

5–20

Chapter 5: Functional Description—ALTMEMPHY

Block Description

External Memory Interface Handbook Volume 3

June 2011

Altera Corporation

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

Read Datapath

This topic describes the read datapath.

Arria GX, Arria II GX, HardCopy II, Stratix II, and Stratix II GX Devices

The following section discusses support for DDR/DDR2 SDRAM for

Arria GX, Arria II GX, HardCopy II, Stratix II, and Stratix II GX devices.

The full-rate datapath is similar to the half-rate datapath. The full-rate datapath also

consists of a RAM with the same width as the data input (just like that of the

half-rate), but the width on the data output of the RAM is half that of the half-rate

PHY. The function of the RAM is to transfer the read data from the resynchronization

clock domain to the system clock domain.

The read datapath logic is responsible for capturing data sent by the memory device

and subsequently aligning the data back to the system clock domain. The following

functions are performed by the read datapath:

1. Data capture and resynchronization

2. Data demultiplexing

3. Data alignment

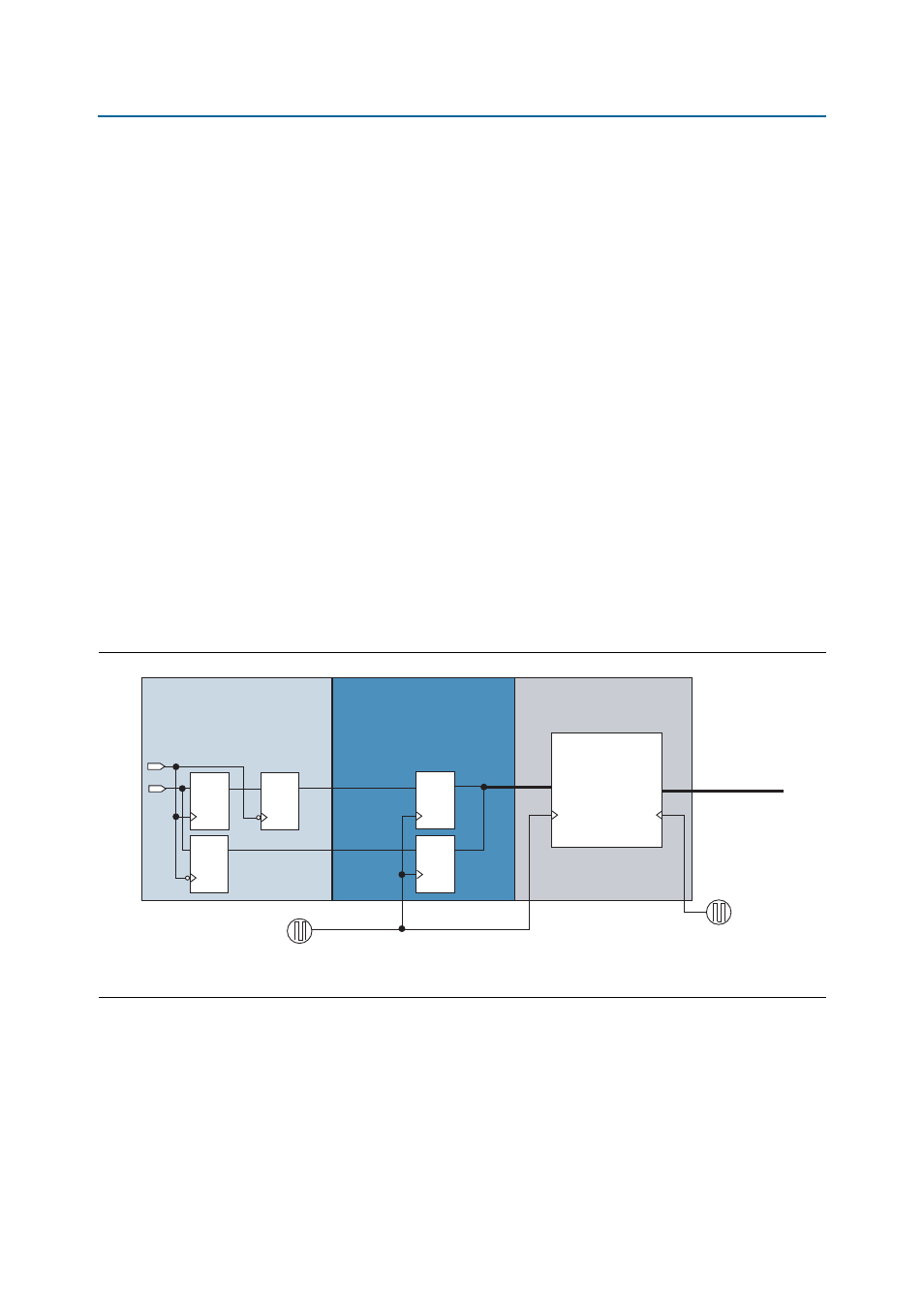

Figure 5–5

shows the order of the functions performed by the read datapath, along

with the frequency at which the read data is handled.

Data Capture and Resynchronization

Data capture and resynchronization is the process of capturing the read data (DQ)

with the DQS strobe and re-synchronizing the captured data to an internal

free-running full-rate clock supplied by the enhanced phase-locked loop (PLL).

The resynchronization clock is an intermediate clock whose phase shift is determined

during the calibration stage.

Figure 5–5. DDR/DDR2 SDRAM Read Datapath in Arria GX, Arria II GX, HardCopy II, Stratix II, and Stratix II GX

Devices

(Note 1)

Note to

Figure 5–5

:

(1) In Arria II GX devices the resynchronization register is implemented in IOE.

SDR

SDR/HDR

DDR

D

Q

D

Q

Data Capture

IOE

D

Q

D

Q

D

Q

Data Resynchronization

Data Demux and Alignment

rdata_1x[4n]

wr_data[2n] rd_data[4n]

wr_clk

rd_clk

FIFO

phy_clk_1x

rdata_2x_p[n]

rdata_2x_n[n]

resync_clk_2x

DQ[n]

DQS