Full-rate write, Full-rate write –8, Figure 8–4. full-rate write operation for hpc ii – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 136

8–

8

Ch

apt

er

8:

T

imin

g

Diagr

a

ms

D

D

R

an

d DDR

2 Hi

gh

-P

erfo

rmance Controllers

II

Ex

ternal Memory

Interfac

e H

andbook

Volu

me 3

Jun

e

2

011

Al

tera Cor

por

atio

n

Secti

o

n

I.

D

DR an

d DDR

2 SDR

A

M Co

ntr

o

lle

rs with ALTMEMPH

Y IP

User G

u

ide

Full-Rate Write

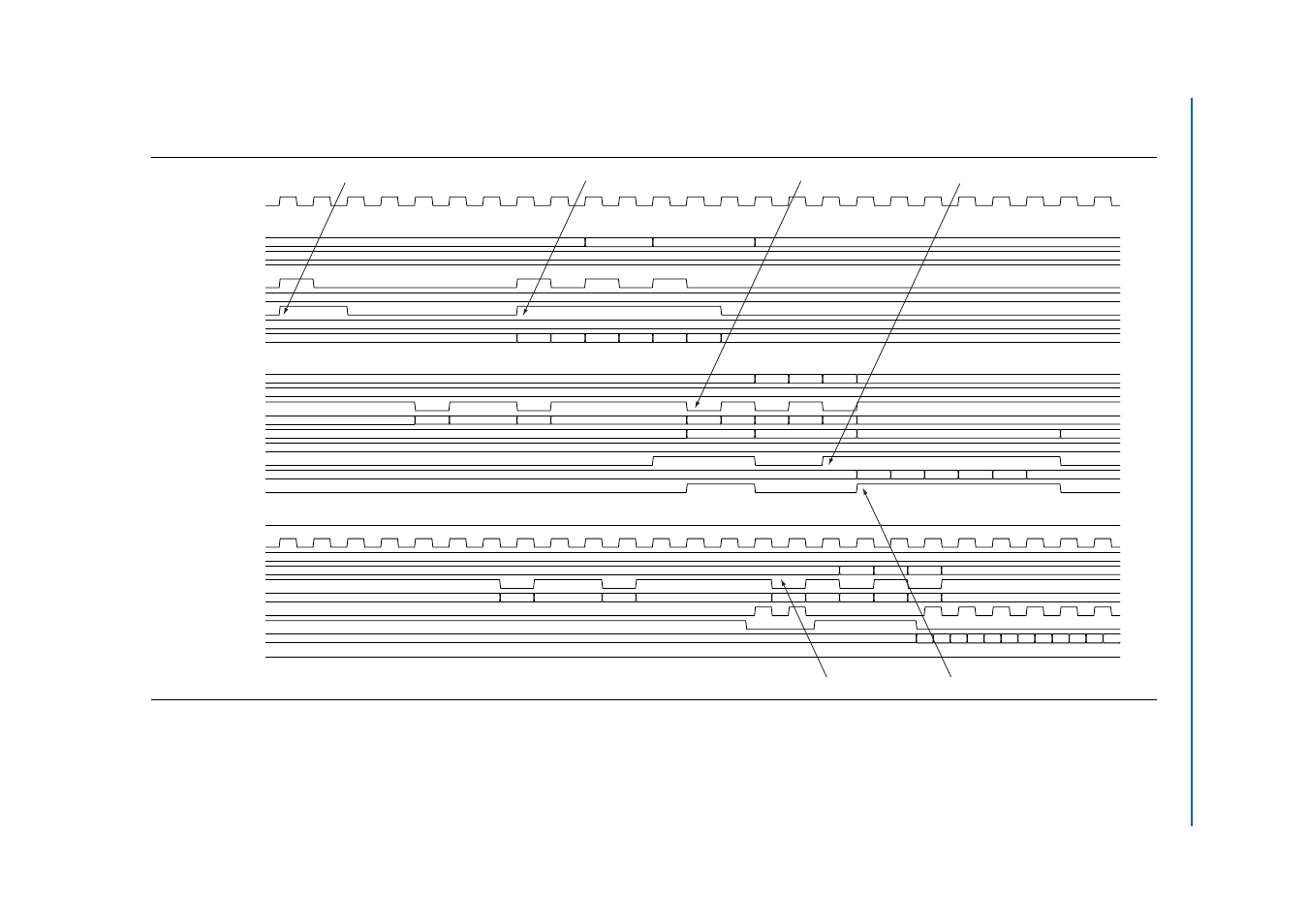

Figure 8–4. Full-Rate Write Operation for HPC II

phy_clk

local_address[23:0]

local_size[2:0]

local_ready

local_burstbegin

local_be[1:0]

local_write_req

local_rdata[15:0]

local_wdata[15:0]

afi_addr[12:0]

afi_ba[1:0][1:0]

afi_cs_n

AFI Command[2:0]

afi_dm[1:0]

afi_wlat[4:0]

afi_dqs_burst

afi_wdata[15:0]

afi_wdata_valid

mem_cke

mem_clk

mem_ba[1:0]

mem_addr[12:0]

mem_cs_n

Mem Command[2:0]

mem_dqs

mem_dm

mem_dq[7:0]

mem_odt

000000

000004

000008

000000

2

3

FFFF

0000

ABCD

EF01

ABCD

EF01

ABCD

EF01

0000

0000

0008

0000

0010

0000

0

NOP

ACT

NOP

WR

NOP

WR

NOP

WR

NOP

WR

NOP

3

0

3

0

3

04

0000

ABCD

EF01

ABCD

EF01

ABCD

EF01

0

0000

0008

0000

0010

0000

NOP

ACT

NOP

WR

NOP

WR

NOP

WR

NOP

WR

NOP

00

CD AB

01

EF CD AB

01

EF

CD AB

01

EF

Local Interface

Controller - AFI

AFI Memory Interface

[5]

[3]

[2]

[1]

[6]

[4]