Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 52

5–6

Chapter 5: Functional Description—ALTMEMPHY

Block Description

External Memory Interface Handbook Volume 3

June 2011

Altera Corporation

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

1

If the design cascades PLLs, the source (upstream) PLL should have a low-bandwidth

setting; the destination (downstream) PLL should have a high-bandwidth setting.

Adjacent PLLs cascading is recommended to reduce clock jitters.

f

For more information about the VCO frequency range and the available phase shifts,

refer to the PLLs in Stratix II and Stratix II GX Devices chapter in the respective device

family handbook.

shows the clock outputs for Arria GX, HardCopy II, Stratix II, and

Stratix II GX devices.

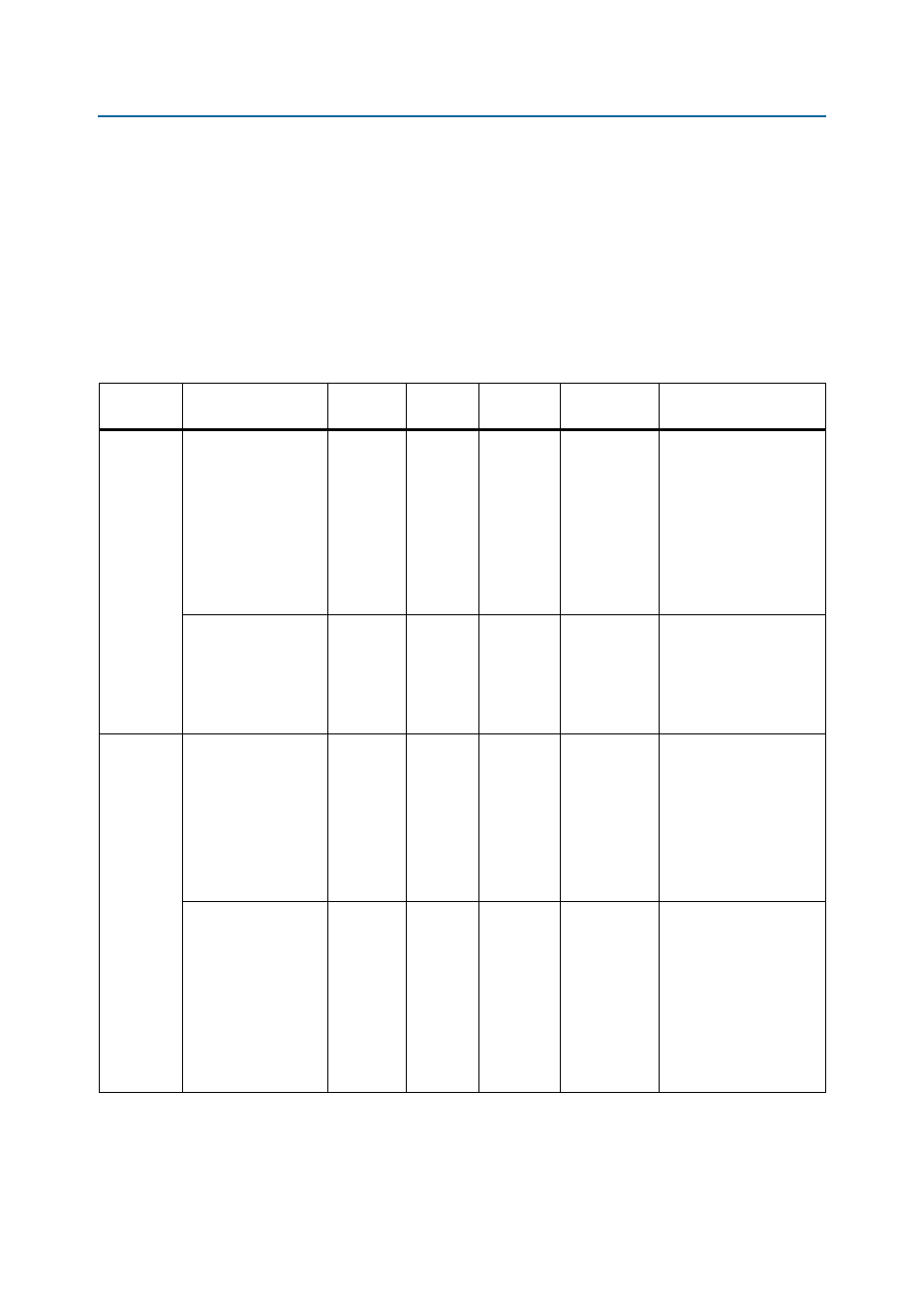

Table 5–1. DDR/DDR2 SDRAM Clocking in Arria GX, HardCopy II, Stratix II, and Stratix II GX Devices (Part 1 of 3)

Design

Rate

Clock Name

Postscale

Counter

Phase

(Degrees)

Clock Rate

Clock

Network Type

Notes

Half-rate

phy_clk_1x

and

aux_half_rate_clk

C0

0

Half-Rate

Global

The only clocks

parameterizable for the

ALTMEMPHY

megafunction. These

clocks also feed into a

divider circuit to provide

the PLL scan_clk signal

(for reconfiguration) that

must be lower than

100 MHz.

mem_clk_2x

and

aux_full_

rate_clk

C1

0

Full-Rate

Global

Clocks DQS and as a

reference clock for the

memory devices.

Full rate

aux_half_rate_clk

C0

0

Half-Rate

Global

The only clock

parameterizable for the

ALTMEMPHY

megafunction. This clock

also feeds into a divider

circuit to provide the PLL

scan_clk

signal (for

reconfiguration) that must

be lower than 100 MHz.

and

mem_clk_2x

and

aux_full_

rate_clk

C1

0

Full-Rate

Global

Clocks DQS and as a

reference clock for the

memory devices.