Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 121

Chapter 6: Functional Description—High-Performance Controller II

6–27

Register Maps

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

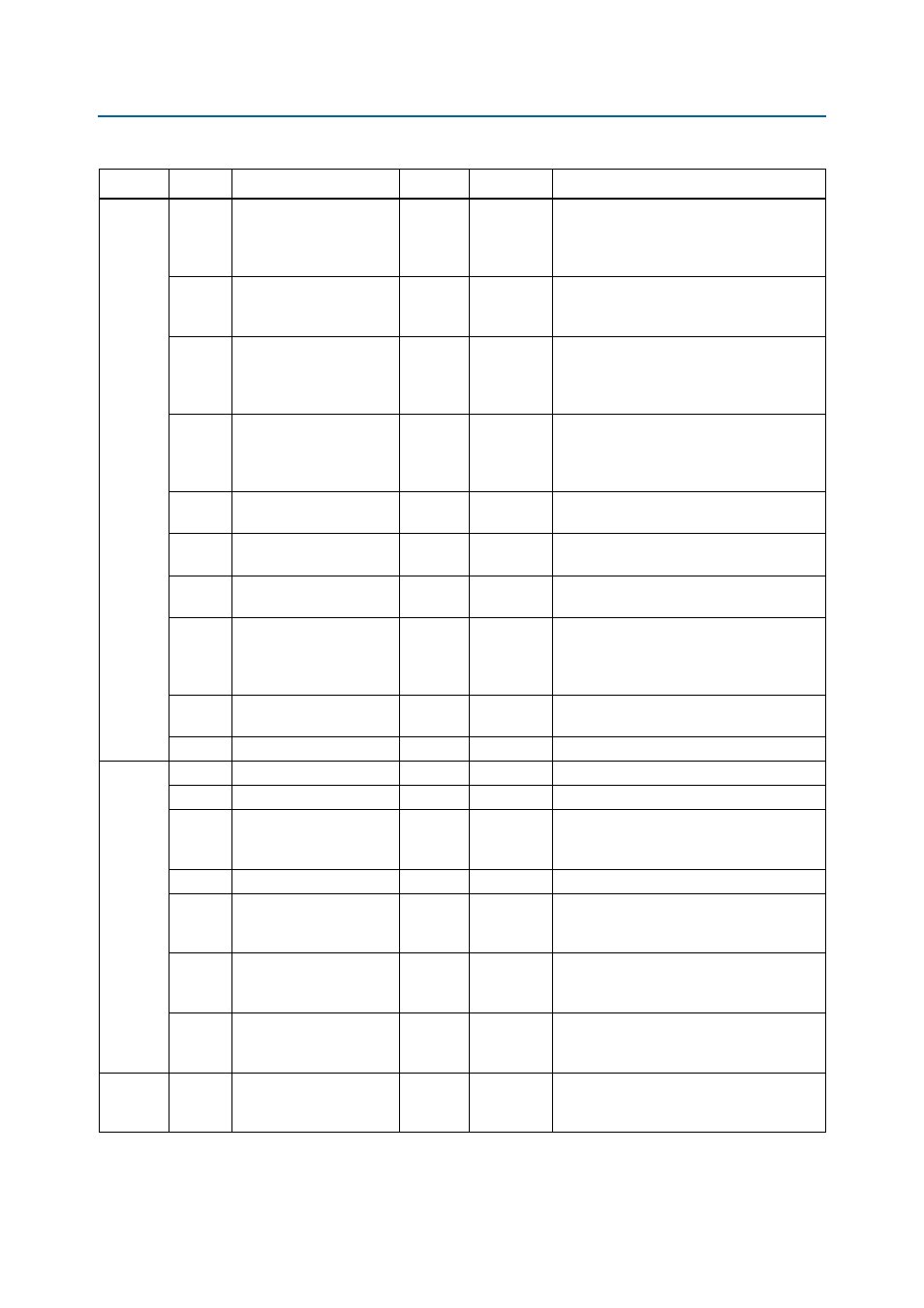

0x130

0

ENABLE_ECC

1

Read write

When this bit equals 1, it enables the

generation and checking of ECC. This bit is

only active if ECC was enabled during IP

parameterization.

1

ENABLE_AUTO_CORR

—

Read write

When this bit equals 1, it enables

auto-correction when a single-bit error is

detected.

2

GEN_SBE

0

Read write

When this bit equals 1, it enables the

deliberate insertion of single-bit errors, bit 0,

in the data written to memory. This bit is

used only for testing purposes.

3

GEN_DBE

0

Read write

When this bit equals 1, it enables the

deliberate insertion of double-bit errors, bits

0 and 1, in the data written to memory. This

bit is used only for testing purposes.

4

ENABLE_INTR

1

Read write

When this bit equals 1, it enables the

interrupt output.

5

MASK_SBE_INTR

0

Read write

When this bit equals 1, it masks the

single-bit error interrupt.

6

MASK_DBE_INTR

0

Read write

When this bit equals 1, it masks the

double-bit error interrupt

7

CLEAR

0

Read write

When this bit equals 1, writing to this

self-clearing bit clears the interrupt signal,

and the error status and error address

registers.

8

MASK_CORDROP_INTR

0

Read write

When this bit equals 1, the dropped

autocorrection error interrupt is dropped.

9

Reserved.

0

—

Reserved for future use.

0x131

0

SBE_ERROR

0

Read only

Set to 1 when any single-bit errors occur.

1

DBE_ERROR

0

Read only

Set to 1 when any double-bit errors occur.

2

CORDROP_ERROR

0

Read only

Value is set to 1 when any

controller-scheduled autoconnections are

dropped.

7:3

Reserved.

0

—

Reserved for future use.

15:8

SBE_COUNT

0

Read only

Reports the number of single-bit errors that

have occurred since the status register

counters were last cleared.

23:16

DBE_COUNT

0

Read only

Reports the number of double-bit errors that

have occurred since the status register

counters were last cleared.

31:24

CORDROP_COUNT.

0

Read only

Reports the number of controller-scheduled

autocorrections dropped since the status

register counters were last cleared.

0x132

31:0

ERR_ADDR

0

Read only

The address of the most recent ECC error.

This address is a memory burst-aligned local

address.

Table 6–15. Controller Register Map (Part 4 of 5)

Address

Bit

Name

Default

Access

Description