Rockwell Automation 20D PowerFlex 700S Drive Ph I Control, Frames 1...11 User Manual

Page 91

Programming and Parameters

3-37

256

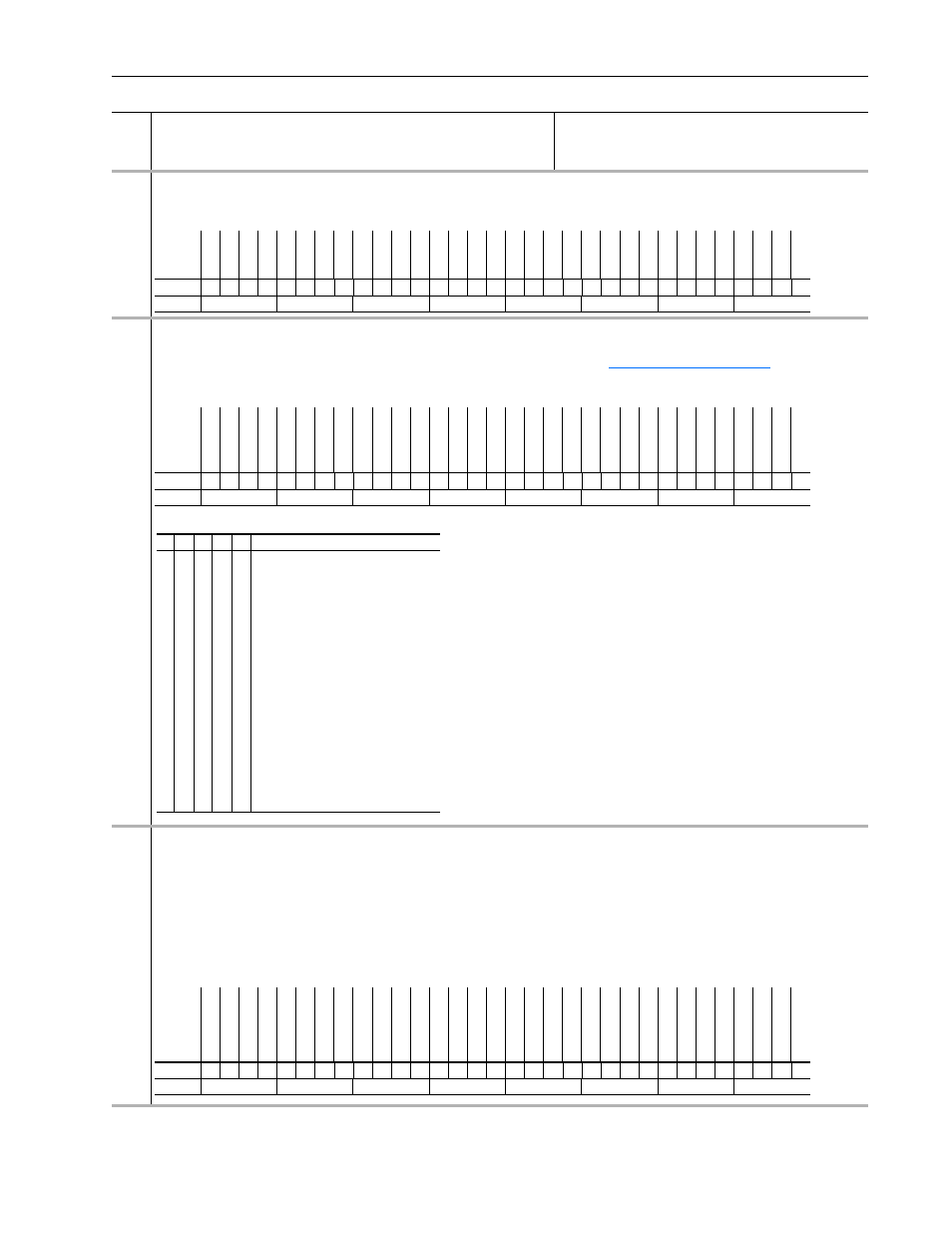

Opt 0 Regis Stat

Indicates the registration control status on port 0 of the feedback option card.

• Bit 0 [Armed] indicates the registration latch is armed.

• Bit 1 [Found] indicates the registration event has triggered the latch.

259

Hi Res0 Config

Specifies the configuration options for the Hi-Resolution Encoder Feedback Option.

• Bit 5 [Hi Res Dir] determines the counting direction. If clear, the direction is forward or up. If set, the direction is reverse or down.

• Bits12 [SmplRate bt0] -15 [SmplRate bt3] configure the sample interval for measuring speed (See

Table 259: Encoder Sample Interval

). Increasing the

encoder sample interval improves speed measurement near zero speed. Decreasing allows the speed control regulator to perform with high gains at high

speeds.

260

Hi Res0 Status

Indicates faults on the Hi-Resolution Encoder Feedback Option.

• Bit 8 [Open Wire] indicates an open wire fault. The feedback option card checks for a pre-determined constant value. If this value is not within tolerances, an

open wire fault is declared. A quadrature check is also done. If an error occurs during the check, the open wire check is aborted. If 3 quadrature errors occur

in succession, the open wire check will complete and the constant value checked again. If this value is not within tolerances, the fault is declared.

• Bit 9 [Power Fail] indicates the failure of the power supply.

• Bit 10 [Diag Fail] indicates the option board failed its power-up diagnostic test. The pattern on the FPGA must be identical to the pattern written from the DSP,

or the board status test will fail.

• Bit 11 [Msg Checksum] indicates a message checksum fault. The check sum associated with the Heidanhain encoder must be correct and acknowledged by

the feedback option card.

• Bit 12 [Time Out Err] indicates a RS-485 time-out fault. This check requires information to be sent from the encoder to the feedback option card within a

specified time. Typical times are about 10 clock cycles before and error is detected. This check is done only at power-up.

No.

Name

Description

Values

Li

nkab

le

Read

-Wr

it

e

Da

ta

T

ype

Options

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

F

ound

Ar

med

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True

Options

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

SmplRate b

t3

SmplRate b

t2

SmplRate b

t1

SmplRate b

t0

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

SW Re

set

Hi Res

D

ir

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Default

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True

Table 259: Encoder Sample Interval

Bit 15 14 13 12 Encoder Sample Interval Settings

0

0

0

0 0.5 ms

0

0

0

1 0.5 ms (min. setting)

0

0

1

0 1.0 ms

0

0

1

1 1.5 ms

0

1

0

0 2.0 ms (default setting)

0

1

0

1 2.5 ms

0

1

1

0 3.0 ms

0

1

1

1 3.5 ms

1

0

0

0 4.0 ms

1

0

0

1 4.5 ms

1

0

1

0 5.0 ms

1

0

1

1 5.5 ms

1

1

0

0 6.0 ms (max. setting)

1

1

0

1 6.0 ms

1

1

1

0 6.0 ms

1

1

1

1 6.0 ms

Options

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Time Ou

t Err

Msg Chec

ksu

m

Dia

g F

ail

Po

w

er

F

ai

l

Open Wir

e

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True