Rockwell Automation 20D PowerFlex 700S Drive Ph I Control, Frames 1...11 User Manual

Page 90

3-36

Programming and Parameters

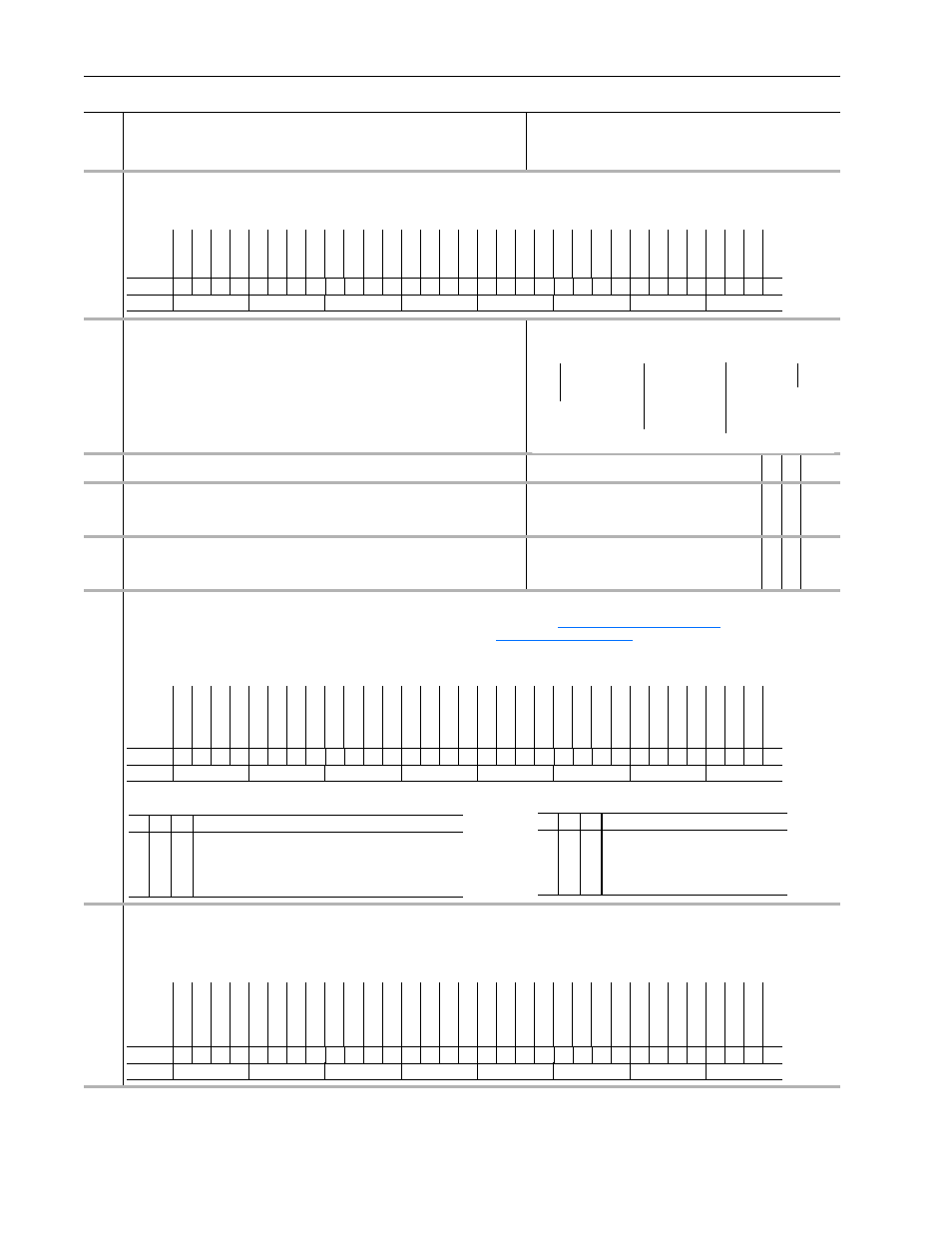

248

Port1 Regis Stat

Indicates the registration control status of port 0.

• Bit 0 [Armed] indicates the registration latch is armed.

• Bit 1 [Found] indicates the registration event has triggered the latch.

249

Fdbk Option ID

Displays information about the Feedback Option.

• Bits 15-11 indicate Module ID Number.

• Bits 10-6 indicate Version Number.

• Bits 5-3 indicate Revision Number High.

• Bits 2-0 indicate Revision Number Low.

Hexadecimal 1000 indicates resolver, hexadecimal 2000 indicates old high-resolution

board, and hexadecimal 2040 indicates new high-resolution board.

Options:

250

FB Opt0 Posit

Displays the position feedback (accumulator) from the feedback option card port 0.

Default:

Min/Max:

0

-/+2147483648

32-bit

Integer

251

FB Opt0 Spd Fdbk

Displays the speed feedback from the feedback option card port 0.

Units:

Default:

Min/Max:

Comm Scale:

RPM

0.0000

-/+14000.0000

Par 4 [Motor NP RPM] = 1.0

Floating

Point

253

Opt 0 Regis Ltch

Displays the registration data of the feedback option card port 0. The registration data is

the position reference counter value latched by the external strobes. The strobe signal

used to trigger the latch is configurable by the Par P254 [Opt 0 Regis Cnfg].

Default:

Min/Max:

0

-/+2147483648

32-bit

Integer

254

Opt 0 Regis Cnfg

Configures the registration latch for port 0 of the feedback option card.

• Bits 3 [RL Trig Edg0] and 4 [RL Trig Edg1] select which trigger edges signal the position (see

Table 254A: Trigger Source Settings

).

• Bits 5 [RL Dir Rev] and 6 [RL Dir Fwd] set the direction of position capture (see

Table 254B: Direction Settings

• Bits 8 [RL Filt bit0] -11 [RL Filt bit3] configure a digital filter for the registration trigger signal. This filter can be used to reject spurious noise. The filter works

by waiting a programmed time before deciding that the signal is valid. This waiting imposes a mandatory delay in the registration signal. The filter delay is

programmable in increments of 100 nanoseconds from 0 (or no delay) up to 700 nanoseconds.

255

Opt 0 Regis Ctrl

Configures the registration control on port 0 of the feedback option card.

• Set bit 0 [Arm Request] to arm the registration logic for the next trigger event. The particular latch will be armed and ready to be strobed on the next

occurrence of the trigger input.

• Set bit 1 [DisArm Req] to disarm the registration logic for next trigger event.

No.

Name

Description

Values

Li

nkab

le

Read

-Wr

it

e

Da

ta

T

ype

Options

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Ar

m

ed

F

oun

d

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True

N N NNN

N N NNN

N NNN

Module ID No.

Version No.

Revision No. Low

N NNN

Revision No. High

Options

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

Reser

ved

R

L Fi

lt bi

t3

R

L Fi

lt bi

t2

R

L Fi

lt bi

t1

R

L Fi

lt bi

t0

Reser

ved

RL D

ir

Fwd

RL D

ir

Re

v

RL T

rig

Ed

g1

RL T

rig

Ed

g0

Reser

ved

Reser

ved

Reser

ved

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

1

1

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True

Table 254A: Trigger Source Settings

Bit

4

3

0

0 Capture position on rising edge

0

1 Capture position on falling edge

1

0 Capture position on both edges

1

1 Disable capture

Table 254B: Direction Settings

Bit

6

5

0

0 Disable capture

0

1 Capture position during Reverse rotation

1

0 Capture position during Forward rotation

1

1 Capture position during either rotation

Options

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Res

er

ved

Disar

m Req

Ar

m Re

ques

t

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True