Rockwell Automation 20D PowerFlex 700S Drive Ph I Control, Frames 1...11 User Manual

Page 87

Programming and Parameters

3-33

236

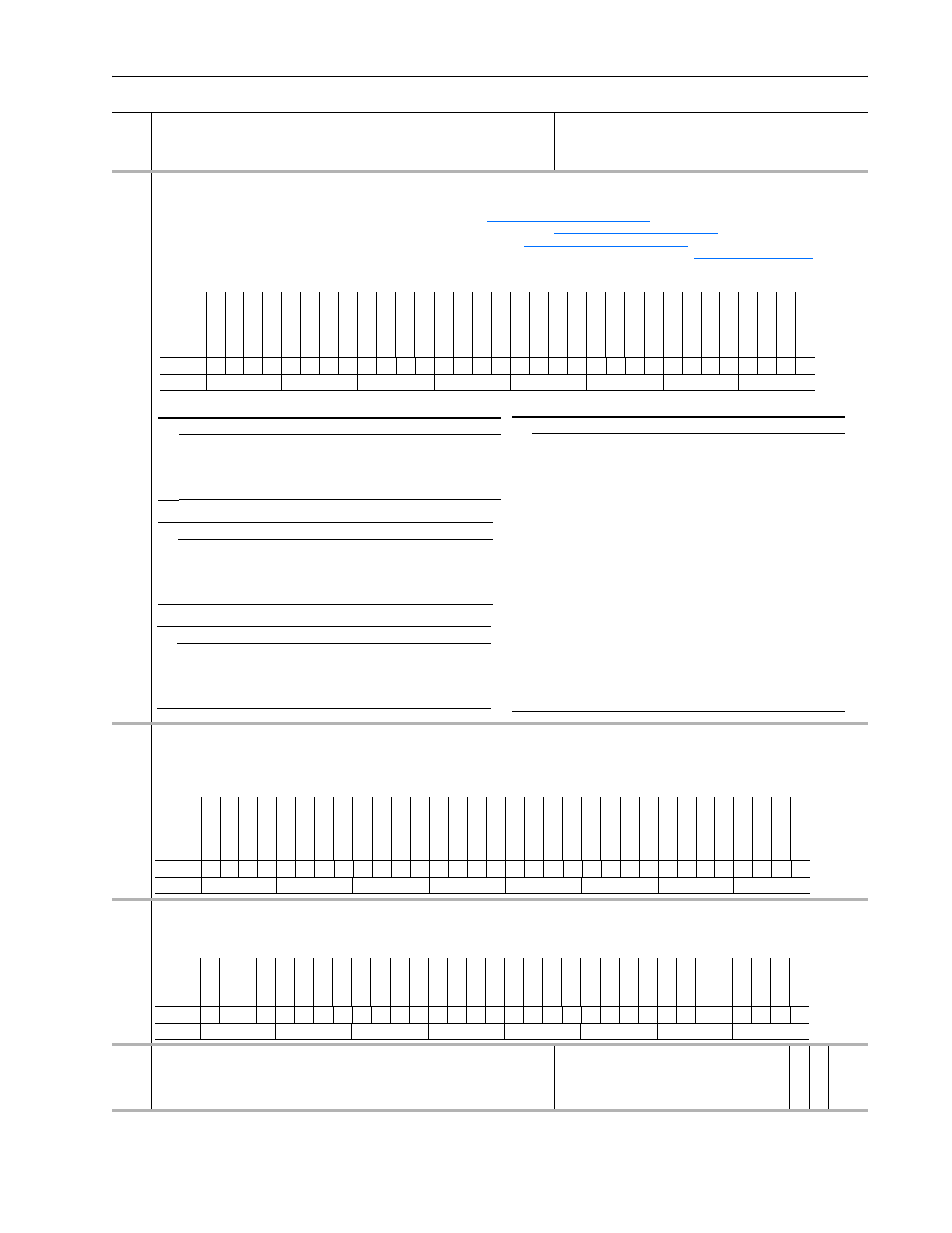

Port0 Regis Cnfg

Configures the registration latch at port 0.

• Bit 0 [RL Encdr1 Sel] selects the encoder for the input source of latched data. Setting bit 0 selects Encoder 1, resetting the bit to zero selects Encoder 0.

• Bits 1 [RL Trig Src0] and 2 [RL Trig Src1] select the trigger source (see

Table 236A: Trigger Source Settings

).

• Bits 3 [RL Trig Edg0] and 4 [RL Trig Edg1] select which edges signal the position (see

Table 236B: Edge Selection Settings

).

• Bits 5 [RL Dir Rev] and 6 [RL Dir Fwd] set the direction of position capture (see

Table 236C: Trigger Source Settings

• Bits 8 [DI Filt bt0], 9 [DI Filt bit1], 10 [DI Filt bt2], and 11 [DI Filt bit3] configure a filter for the digital input 1 and 2 (see

). The filter

requires the input signal to be stable for the specified time period. Input transitions within the filter time setting will be ignored.

237

Port0 Regis Ctrl

Configures the registration control for port 0.

• Set bit 0 [Arm Request] to arm the registration logic for the next trigger event. The particular latch will be armed and ready to be strobed on the next

occurrence of the trigger input.

• Set bit 1 [DisArm Req] to disarm the registration logic for next trigger event.

238

Port0 Regis Stat

Indicates the registration control status of port 0.

• Bit 0 [Armed] indicates the registration latch is armed.

• Bit 1 [Found] indicates the registration event has triggered the latch.

240

Encdr1 Position

Displays the position feedback (accumulator) from Encoder 1. The value changes by a

value of 4 times the Pulses Per Revolution (PPR) rating of the encoder for each full

revolution of the encoder shaft. Used by the VPL to close the position loop if the position

control is selected.

Default:

Min/Max:

0

-/+2147483648

32-bit

Integer

No.

Name

Description

Values

Li

nkab

le

Read

-Wr

it

e

Da

ta

T

ype

Table 236A: Trigger Source Settings

Bit 2 1

0 0

Digital Input 2 AND Encoder 0 (Primary Encoder) Z Phase

0 1

Digital Input 3 (default setting)

1 0

Digital Input 2

1 1

Encoder 0 (Primary Encoder) Z Phase

Table 236C: Trigger Source Settings

Bit 6

5

0

0

Disable capture

0

1

Capture position during Reverse rotation

1

0

Capture position during Forward rotation

1

1

Capture position during either rotation

Table 236D: Filter Settings

Bit 11 10 9

8

Input Filter Setting

0

0

0

0

Filter disabled

0

0

0

1

100 ns filter

0

0

1

0

200 ns filter

0

0

1

1

300 ns filter

0

0

1

1

300 ns filter

0

1

0

0

400 ns filter

0

1

0

1

500 ns filter

0

1

1

0

600 ns filter

0

1

1

1

700 ns filter

1

0

0

0

800 ns filter (default setting)

1

0

0

1

900 ns filter

1

0

1

0

1000 ns filter

1

0

1

1

1100 ns filter

1

1

0

0

1200 ns filter

1

1

0

1

1300 ns filter

1

1

1

0

1400 ns filter

1

1

1

1

1500 ns filter

Options

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

DI

Filt

bit

3

DI

Filt

bit

2

DI

Filt

bi1

DI

Filt

bit

0

Rese

rv

ed

RL Dir Fwd

RL Dir Re

v

RL T

rig

Ed

g1

RL T

rig

Ed

g0

RL T

rig

Src1

RL T

rig

Src0

RL Encdr1Se

l

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

1

1

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Table 236B: Edge Selection Settings

Bit 4

3

0

0

Capture position on rising edge

0

1

Capture position on falling edge

1

0

Capture position on both edges

1

1

Disable capture

0 = False

1 = True

Options

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Dis

ar

m

R

eq

Ar

m Req

ues

t

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True

Options

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

Rese

rv

ed

F

oun

d

Ar

m

ed

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True