Rainbow Electronics DS3134 User Manual

Page 95

DS3134

95 of 203

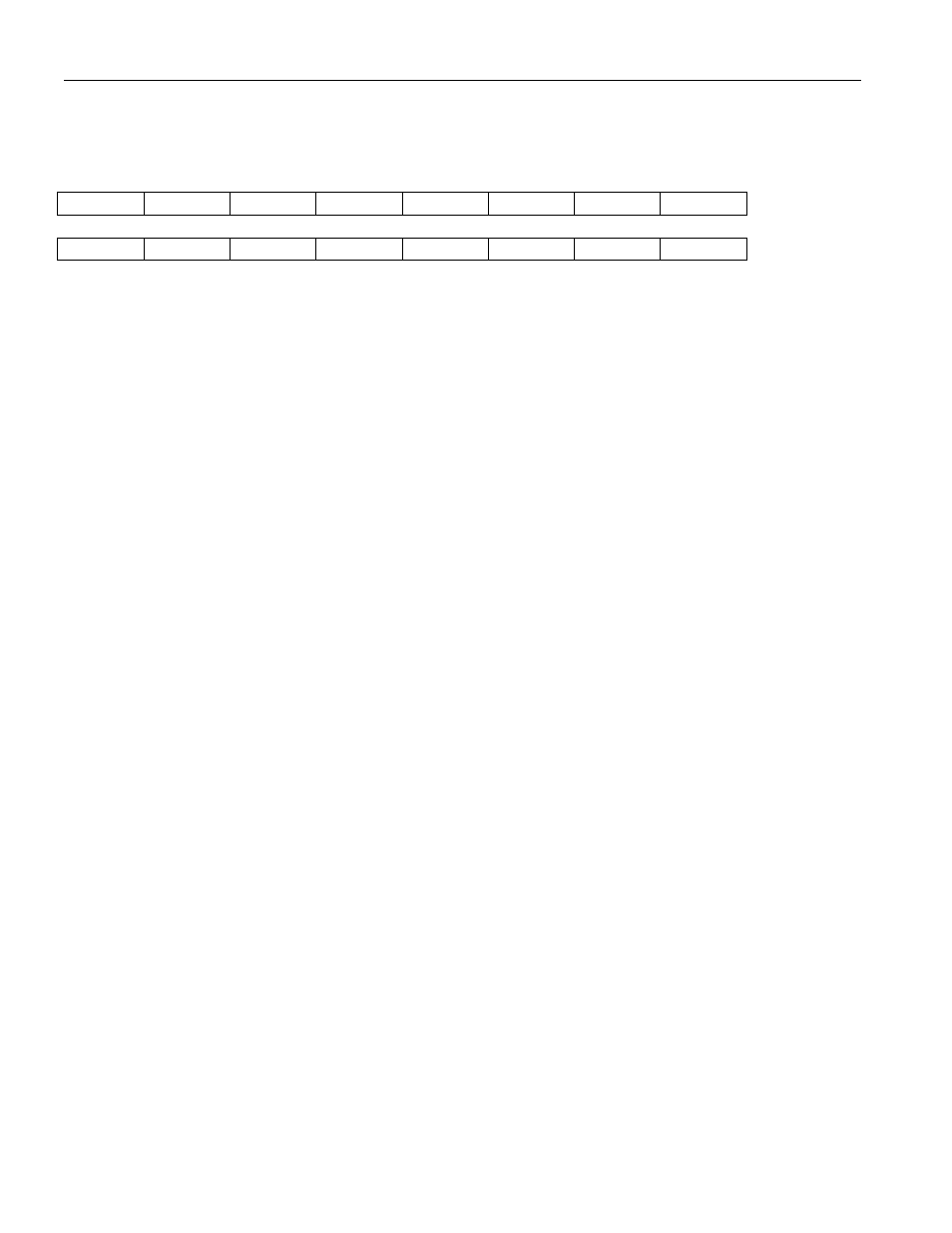

Register Name:

TFLWM

Register Description: Transmit FIFO Low Water Mark

Register Address:

09A4h

7

6

5

4

3

2

1

0

TLWM7

TLWM6

TLWM5

TLWM4

TLWM3

TLWM2

TLWM1

TLWM0

15

14

13

12

11

10

9

8

n/a

n/a

n/a

n/a

n/a

n/a

TLWM9

TLWM8

Note: Bits that are underlined are read only, all other bits are read-write.

Bits 0 to 9 / Low Water Mark (TLWM0 to TLWM9). These 10 bits indicate the setting of the

Transmit Low Water Mark. The Low Water Mark setting is the number of Blocks left in the Transmit

FIFO before the DMA will get more data from the PCI Bus. The Low Water Mark setting must be

between (inclusive) 1 block and one less than the number of blocks in the link list chain for the particular

channel involved. For example, if five blocks are linked together, then the Low Water Mark can be set to

1, 2, or 3. In another words the Low Water Mark can be set at a value of 1 to N – 2, where N = number of

blocks are linked together. Any other numbers are illegal.

0000000000 (000h) = invalid setting

0000000001 (001h) = Low Water Mark is 1 Block

0000000010 (002h) = Low Water Mark is 2 Blocks

0111111111 (1FFh) = Low Water Mark is 511 Blocks

1111111111 (3FFh) = Low Water Mark is 1023 Blocks