Pci bus arbitration, Pci initiator abort figure 9.1e – Rainbow Electronics DS3134 User Manual

Page 148

DS3134

148 of 203

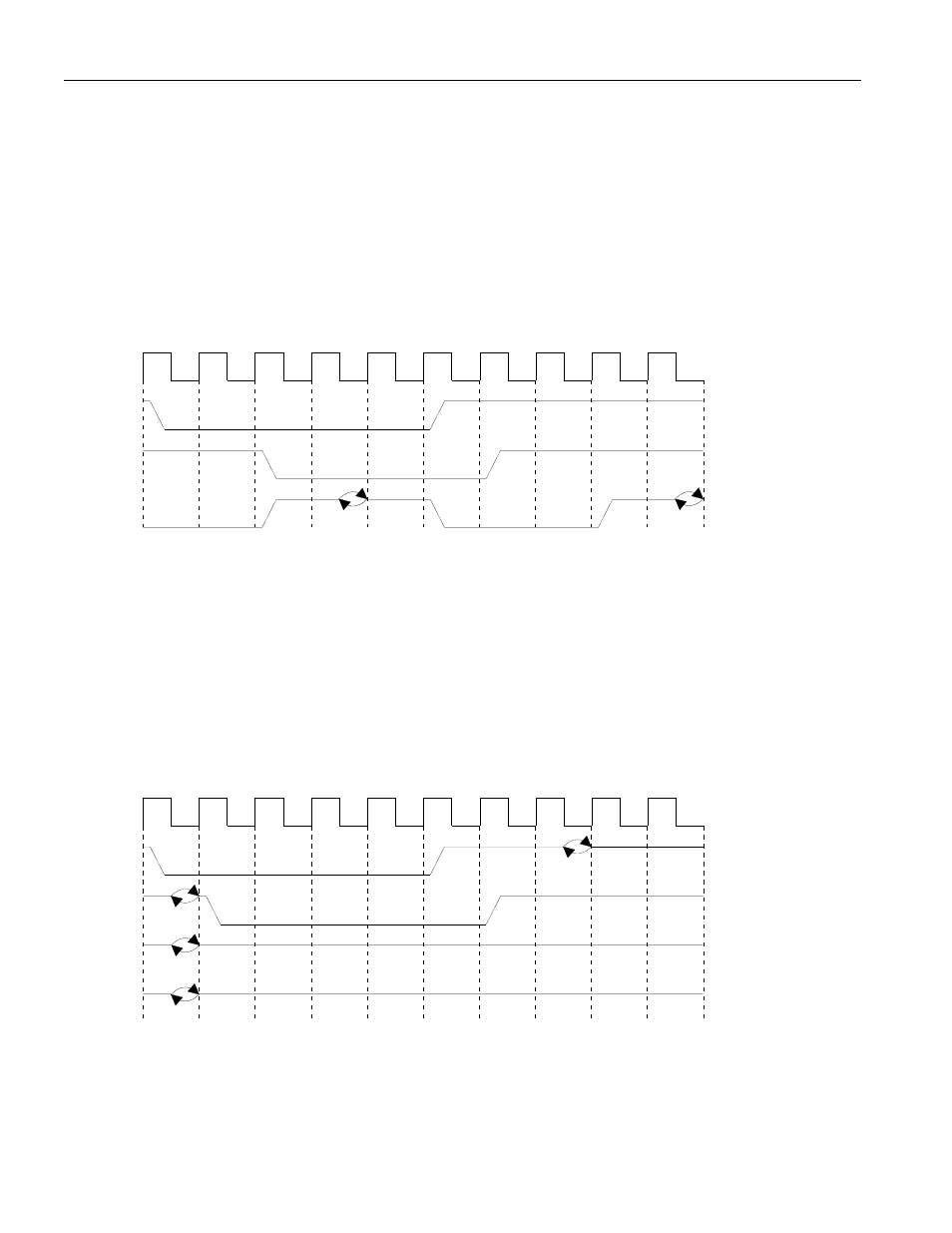

PCI Bus Arbitration

The PCI bus can be arbitrated as shown in Figure 9.1D. The initiator will request bus access by asserting

PREQ*. A central arbiter will grant the access some time later by asserting PGNT*. Once the bus has

been granted, the initiator will wait until both PIRDY* and PFRAME* are deasserted (i.e. an idle cycle)

before acquiring the bus and beginning the transaction. As shown in Figure 9.1C, the bus was still being

used when it was granted and the device had to wait until clock cycle #6 before it acquired the bus and

begin the transaction. The arbiter can deassert PGNT* at any time and the initiator must relinquish the

bus after the current transfer is complete (which can be limited by the latency timer).

PCI Bus Arbitration Signaling Protocol Figure 9.1D

PCI Initiator Abort

If a target fails to respond to an initiator by asserting PDEVSEL* and PTRDY* within 5 clock cycles,

then the initiator will abort the transaction by deasserting PFRAME* and then one clock later deasserting

PIDRY* (see Figure 9.1E). If such a scenario occurs, it will be reported via the Master Abort status bit in

the PCI Command/Status configuration register (see Section 9.2).

PCI Initiator Abort Figure 9.1E

1

2

3

4

5

6

7

8

9

10

PCLK

PREQ*

PGNT*

PFRAME*

pci_arb

Bus is

Relinquished

Bus is Acquired

Wait for PGNT* Asserted

and then PFRAME* &

PIRDY* Deasserted

1

2

3

4

5

6

7

8

9

10

PCLK

PFRAME*

PIRDY*

PTRDY*

PDEVSEL*

pci_iabt