Rainbow Electronics DS3134 User Manual

Page 134

DS3134

134 of 203

Pending Queue Burst Reading

The DMA has the ability to read the Pending Queue in bursts. This allows for a more efficient use of the

PCI Bus. The DMA can grab descriptors from the Pending Queue in-groups rather than one at a time,

freeing up the PCI Bus for more time critical functions.

Internal to the device there is a FIFO that can store up to 16 Pending Queue Descriptors (16 dwords since

each descriptor occupies one dword). The Host must configure the Pending Queue FIFO for proper

operation via the Transmit DMA Queues Control (TDMAQ) register (see below).

When enabled via the Transmit Pending Queue FIFO Enable (TPQFE) bit, the Pending Queue FIFO will

not read the Pending Queue until it reaches the Low Water Mark. When the Pending Queue FIFO reaches

the Low Water Mark (which is four descriptors), it will attempt to fill the FIFO with additional

descriptors by burst reading the Pending Queue. Before it reads the Pending Queue, it checks (by

examining the Transmit Pending Queue Host Write Pointer) to make sure that the Pending Queue

contains enough descriptors to fill the Pending Queue FIFO. If the Pending Queue does not have enough

descriptors to fill the FIFO, then it will only read enough to empty the Pending Queue. If the FIFO

detects that there are no Pending Queue descriptors available for it to read, then it will wait and try again

later. If the Pending Queue FIFO can read descriptors from the Pending Queue, then it will burst read

them, increment the read pointer, and set the Status Bit for Transmit DMA Pending Queue Read (TPQR)

in the Status Register for DMA (SDMA). See Section 4 for more details on Status Bits.

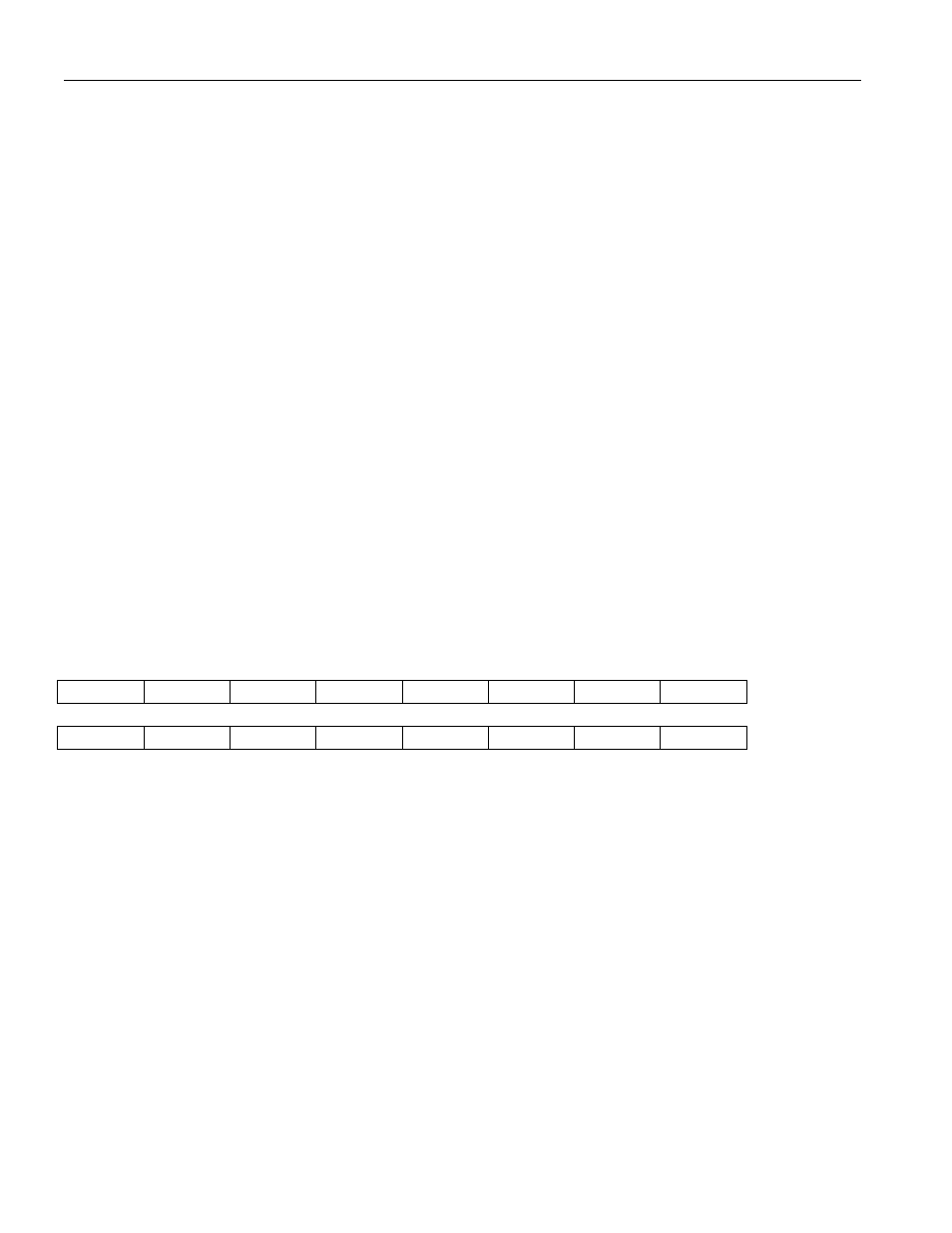

Register Name:

TDMAQ

Register Description: Transmit DMA Queues Control

Register Address:

0880h

7

6

5

4

3

2

1

0

n/a

n/a

n/a

n/a

TDQF

TDQFE

TPQF

TPQFE

15

14

13

12

11

10

9

8

n/a

n/a

n/a

n/a

n/a

TDQT2

TDQT1

TDQT0

Note: Bits that are underlined are read only, all other bits are read-write; default value for all bits is 0.

Bit 0 / Transmit Pending Queue FIFO Enable (TPQFE). To enable the DMA to burst read descriptors

from the Pending Queue; this bit must be set to a one. If this bit is set to zero, descriptors will be read one

at a time.

0 = Pending Queue Burst Read Disabled

1 = Pending Queue Burst Read Enabled

Bit 1 / Transmit Pending Queue FIFO Flush (TPQF). When this bit is set to one, the internal Pending

Queue FIFO will be flushed (currently loaded Pending Queue Descriptors are lost). This bit must be set

to zero for proper operation.

0 = FIFO in normal operation

1 = FIFO is flushed