Rainbow Electronics DS3134 User Manual

Page 179

DS3134

179 of 203

SECTION 11: JTAG

11.1 JTAG DESCRIPTION

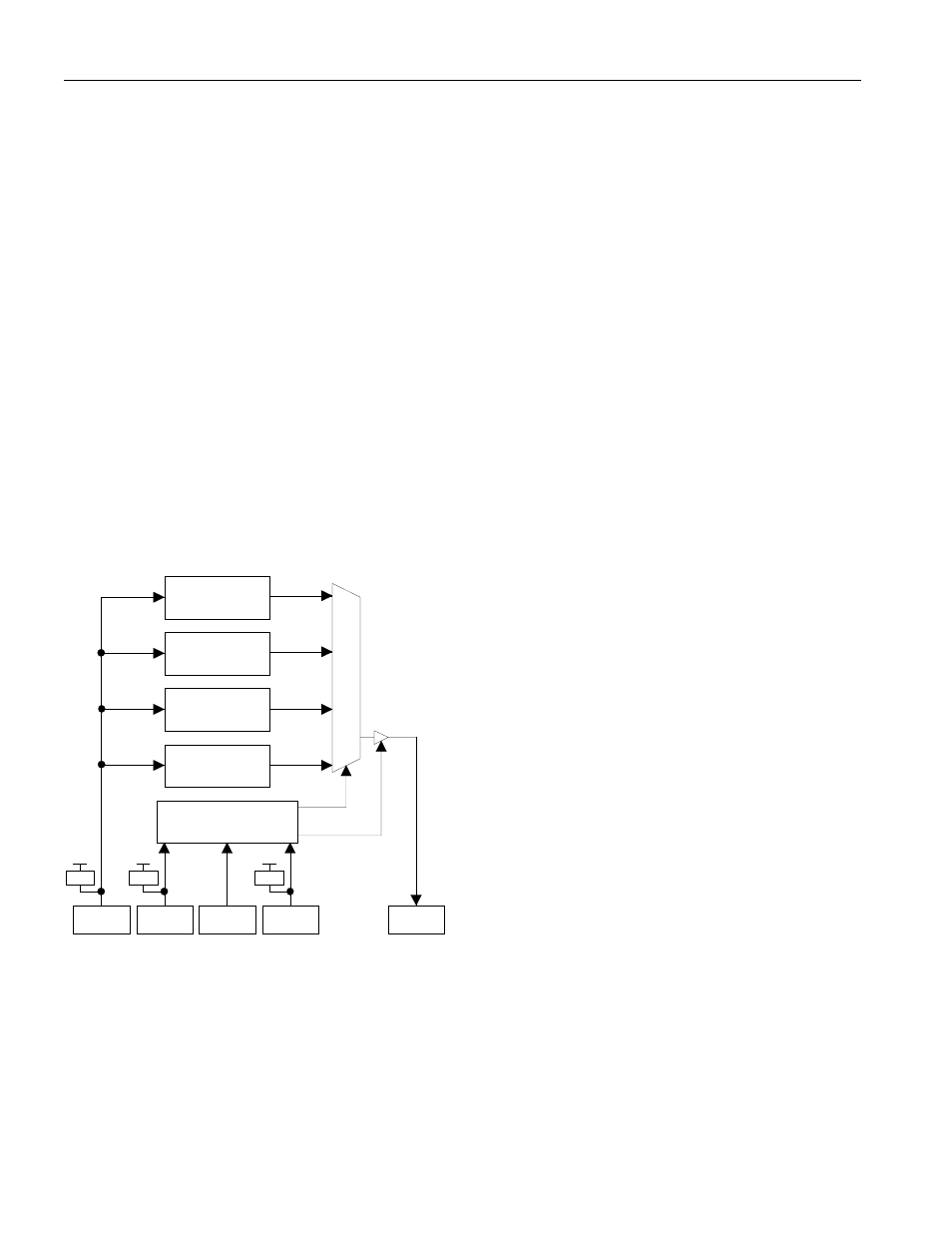

The DS3134 device supports the standard instruction codes SAMPLE/PRELOAD, BYPASS, and

EXTEST. Optional public instructions included are HIGHZ, CLAMP, and IDCODE. See Figure 11.1A

for a Block Diagram. The DS3134 contains the following items, which meet the requirements, set by the

IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture:

Test Access Port (TAP)

TAP Controller

Instruction Register

Bypass Register

Boundary Scan Register

Device Identification Register.

The Test Access Port has the necessary interface pins, namely JTCLK, JTRST*, JTDI, JTDO, and JTMS.

Details on these pins can be found in Section 2.4. Details on the Boundary Scan Architecture and the Test

Access Port can be found in IEEE 1149.1-1990, IEEE 1149.1a-1993, and IEEE 1149.1b-1994.

JTAG Block Diagram Figure 11.1A

11.2 TAP CONTROLLER STATE MACHINE DESCRIPTION

This section covers the details on the operation of the Test Access Port (TAP) Controller State Machine.

Please see Figure 11.2A for details on each of the states described below. The TAP controller is a finite

state machine, which responds to the logic level at JTMS on the rising edge of JTCLK.

Boundary Scan

Register

Identification

Register

Bypass

Register

Instruction

Register

Test Access Port

Controller

Mux

Select

Tri-State

JTDI

10K

JTMS

10K

JTCLK

JTRST*

10K

JTDO

jtag_bd