Rainbow Electronics DS3134 User Manual

Page 33

DS3134

33 of 203

SECTION 3: MEMORY MAP

3.0 INTRODUCTION

All addresses within the memory map on dword boundaries even though all of the internal device

configuration registers are only one word (16 bits) wide. The memory map consumes an address range of

4 kB (12 bits). When the PCI Bus is the Host (i.e. the Local Bus is in the Bridge Mode), the actual 32-bit

PCI Bus addresses of the internal device configuration registers is obtained by adding the DC Base

Address value in the PCI Device Configuration Memory Base Address Register (see Section 9.2 for

details) to the offset listed in Sections 3.1 to 3.11. When an external host is configuring the device via the

Local Bus (i.e. the Local Bus is in the Configuration Mode), the offset is 0h and the Host on the Local

Bus will use the 16-bit addresses listed in Sections 3.1 to 3.11.

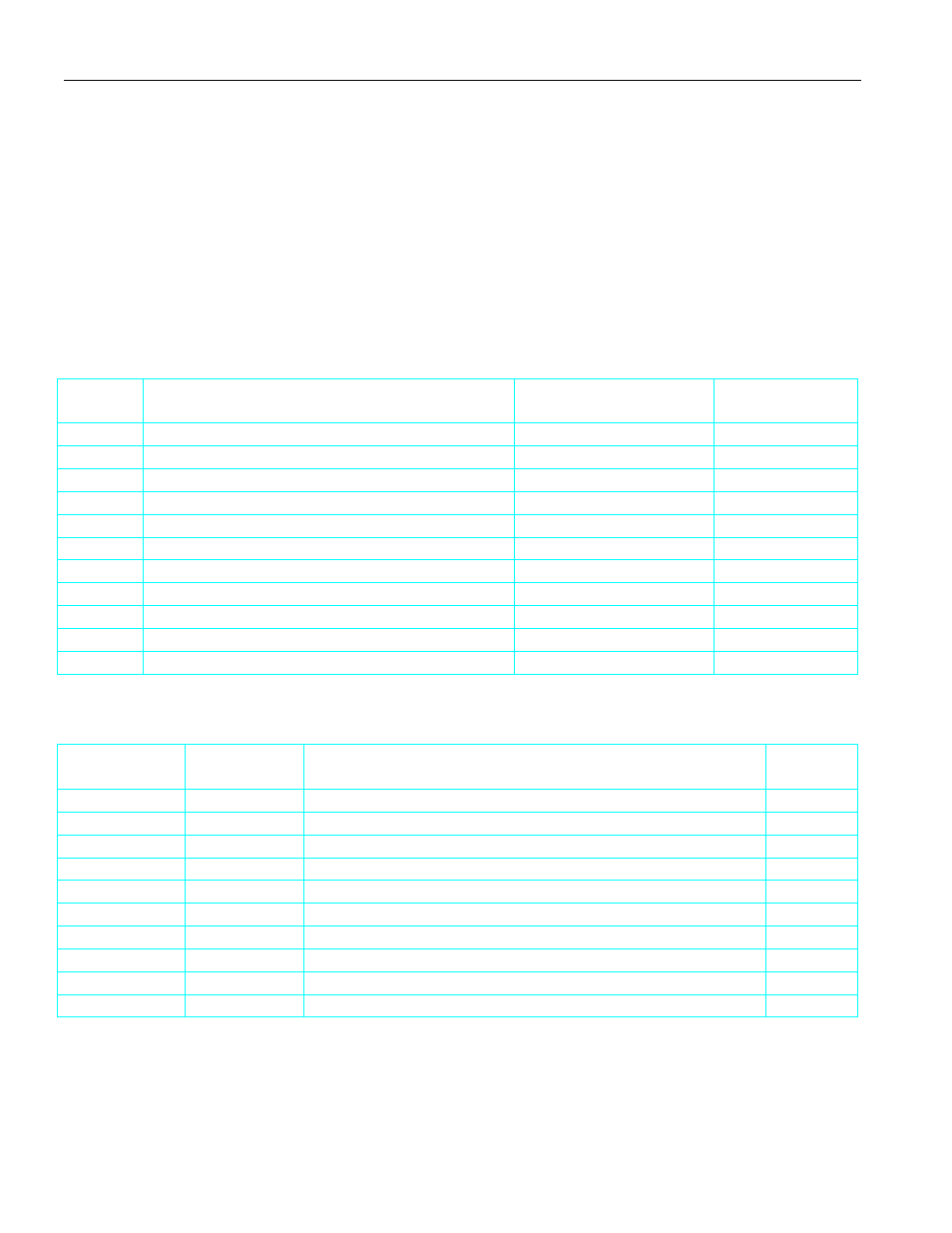

MEMORY MAP ORGANIZATION Table 3.0A

Section

Register Name

PCI Host

[offset from DC Base]

Local Bus Host

(16-bit address)

3.1

General Configuration Registers

(0x000)

(00xx)

3.2

Receive Port Registers

(0x1xx)

(01xx)

3.3

Transmit Port Registers

(0x2xx)

(02xx)

3.4

Channelized Port Registers

(0x3xx)

(03xx)

3.5

HDLC Registers

(0x4xx)

(04xx)

3.6

BERT Registers

(0x5xx)

(05xx)

3.7

Receive DMA Registers

(0x7xx)

(07xx)

3.8

Transmit DMA Registers

(0x8xx)

(08xx)

3.9

FIFO Registers

(0x9xx)

(09xx)

3.10

PCI Configuration Registers for Function 0

(PIDSEL)

(0Axx)

3.11

PCI Configuration Registers for Function 1

(PIDSEL)

(0Bxx)

3.1 GENERAL CONFIGURATION REGISTERS (0XX)

Offset/

Address

Acronym

Register Name

Section

0000

MRID

Master Reset & ID Register.

4.1

0010

MC

Master Configuration.

4.2

0020

SM

Master Status Register.

4.3.2

0024

ISM

Interrupt Mask Register for SM.

4.3.2

0028

SDMA

Status Register for DMA.

4.3.2

002C

ISDMA

Interrupt Mask Register for SDMA.

4.3.2

0030

SV54

Status Register for V.54 Loopback Detector.

4.3.2

0034

ISV54

Interrupt Mask Register for SV54.

4.3.2

0040

LBBMC

Local Bus Bridge Mode Control Register.

10.2

0050

TEST

Test Register.

4.4