Rainbow Electronics DS3134 User Manual

Page 166

DS3134

166 of 203

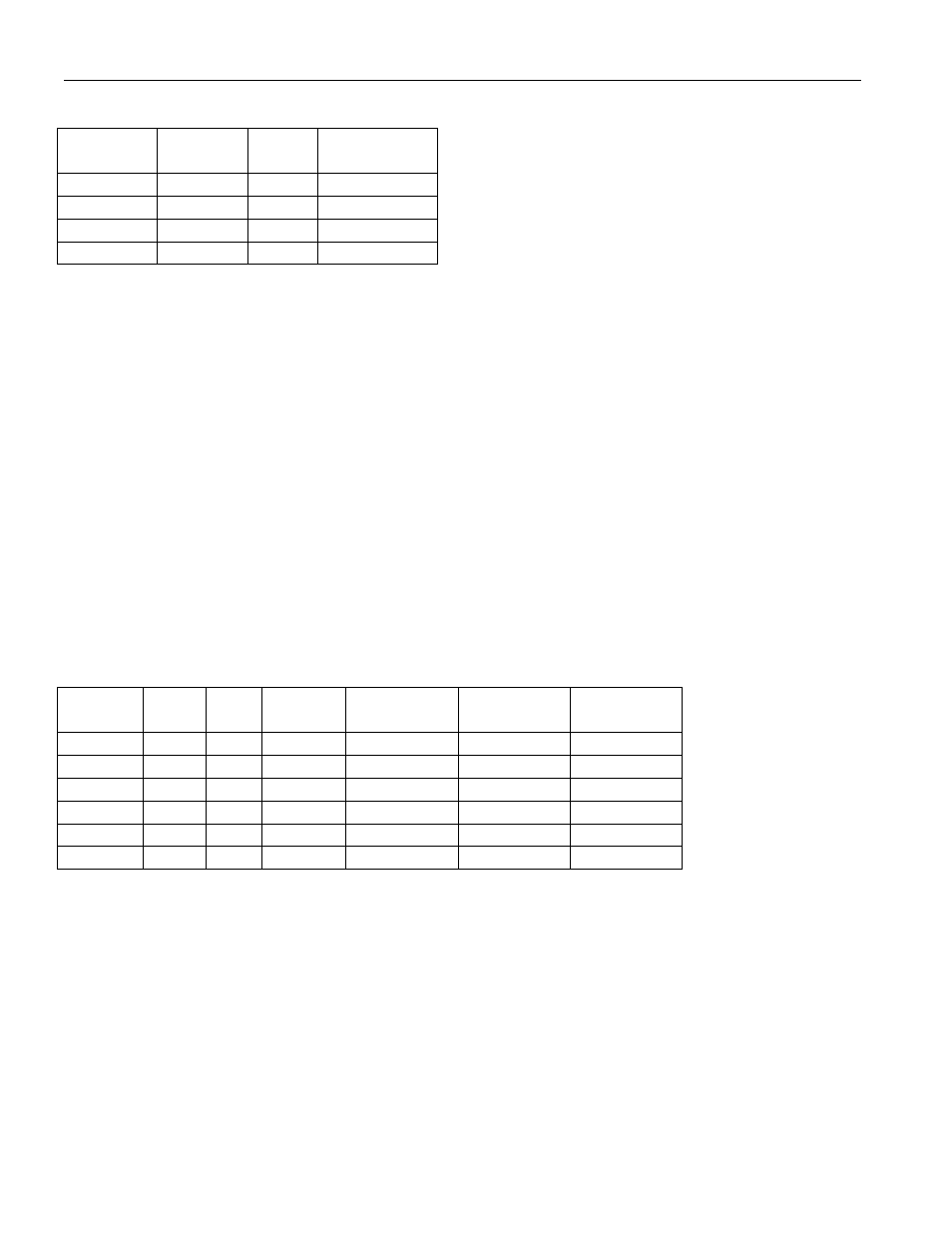

Local Bus 8-Bit Width Address / LBHE* Setting Table 10.1B

PCBE*

[3:0]

A1

A0

LBHE*

1110

0

0

1

1101

0

1

1

1011

1

0

1

0111

1

1

1

Note:

1. All other possible states for PCBE* will cause the device to return a Target Abort to the Host.

2. The 8-bit data picked from the PCI bus will be routed/sample to/from the LD[7:0] signal lines.

3. If no PCBE* signals are asserted during an access, a Target Abort is not return and no transaction

occurs on the Local Bus.

If the Local Bus is to be used as a 16-bit bus, then the LBW control bit must be set to zero. In 16-bit

accesses, by asserting the appropriate PCBE* signals (see Table 10.1C) the Host can either perform a

16-bit access or an 8-bit access. For a 16-bit access, the Host will enable the combination of either

PCBE0*/PCBE1* or PCBE2*/PCBE3* and the Local Bus block will map the word from/to the PCI bus

to/from the LD[15:0] signals. For an 8-bit access in the 16-bit bus mode, the Host must assert just one of

the PCBE0* to PCBE3* signals. If the Host asserts a combination of PCBE* signals not supported by the

Local Bus, then the Local Bus will reject the access and the PCI Block will return a Target Abort to the

Host. See Section 9 for details on a Target Abort. Section 10.3 contains a number of timing examples for

the Local Bus.

Local Bus 16-Bit Width Address / LD / LBHE* Setting Table 10.1C

PCBE*

[3:0]

8/16

A1

A0

LD[15:8]

LD[7:0]

LBHE*

1110

8

0

0

active

1

1101

8

0

1

active

0

1100

16

0

0

active

active

0

1011

8

1

0

active

1

0111

8

1

1

active

0

0011

16

1

0

active

active

0

Note:

1. All other possible states for PCBE* will cause the device to return a Target Abort to the Host.

2. The 16-bit data picked from the PCI bus will be routed/sample to/from the LD[7:0] & LD[15:8] signal

lines as shown.

3. If no PCBE* signals are asserted during an access, a Target Abort is not return and no transaction

occurs on the Local Bus.