Rainbow Electronics DS3134 User Manual

Page 23

DS3134

23 of 203

RS SAMPLED EDGE Table 2.2A

Normal RC Clock Mode

Inverted RC Clock Mode

0 RC Clock Early Mode

falling edge

rising edge

1/2 RC Clock Early Mode

rising edge

falling edge

1 RC Clock Early Mode

falling edge

rising edge

2 RC Clock Early Mode

falling edge

rising edge

Signal Name:

TC0 / TC1 / TC2 / TC3 / TC4 / TC5 / TC6 / TC7 / TC8 / TC9 / TC10 / TC11 /

TC12 / TC13 / TC14 / TC15

Signal Description:

Transmit Serial Clock

Signal Type:

Input

Data can be clocked out of the device either on rising edges (normal clock mode) or falling edges

(inverted clock mode) of TC. This is programmable on a per port basis. TC0 & TC1 can operate at

speeds up to 52 MHz. TC2 to TC15 can operate at speeds up to 10 MHz. If not used, should be tied low.

Signal Name:

TD0 / TD1 / TD2 / TD3 / TD4 / TD5 / TD6 / TD7 / TD8 / TD9 / TD10 / TD11 /

TD12 / TD13 / TD14 / TD15

Signal Description:

Transmit Serial Data

Signal Type:

Output

Can be updated either on the rising edge of TC (normal clock mode) or the falling edge of TC (inverted

clock mode). Data can be forced high.

Signal Name:

TS0 / TS1 / TS2 / TS3 / TS4 / TS5 / TS6 / TS7 / TS8 / TS9 / TS10 / TS11 /

TS12 / TS13 / TS14 / TS15

Signal Description:

Transmit Serial Data Synchronization Pulse

Signal Type:

Input

A one TC clock wide synchronization pulse that can be applied to the Chateau to force byte/frame

alignment. The applied sync signal pulse can be either active high (normal sync mode) or active low

(inverted sync mode). The TS signal can be sampled either on the falling edge or on rising edge of TC

(see Table 2.2B below for details). The applied sync pulse can be during the first TC clock period of a

193/256/512/1024 bit frame or it can be applied 1/2, 1, or 2 TC clocks early. This input sync signal resets

a counter that rolls over at a count of either 193 (T1 mode) or 256 (E1 mode) or 512 (4.096 MHz mode)

or 1024 (8.192 MHz mode) TC clocks. It is acceptable to only pulse the TS signal once to establish byte

boundaries and allow Chateau to keep track of the byte/frame boundaries by counting TC clocks. If the

incoming data does not require alignment to byte/frame boundaries, then this signal should be tied low.

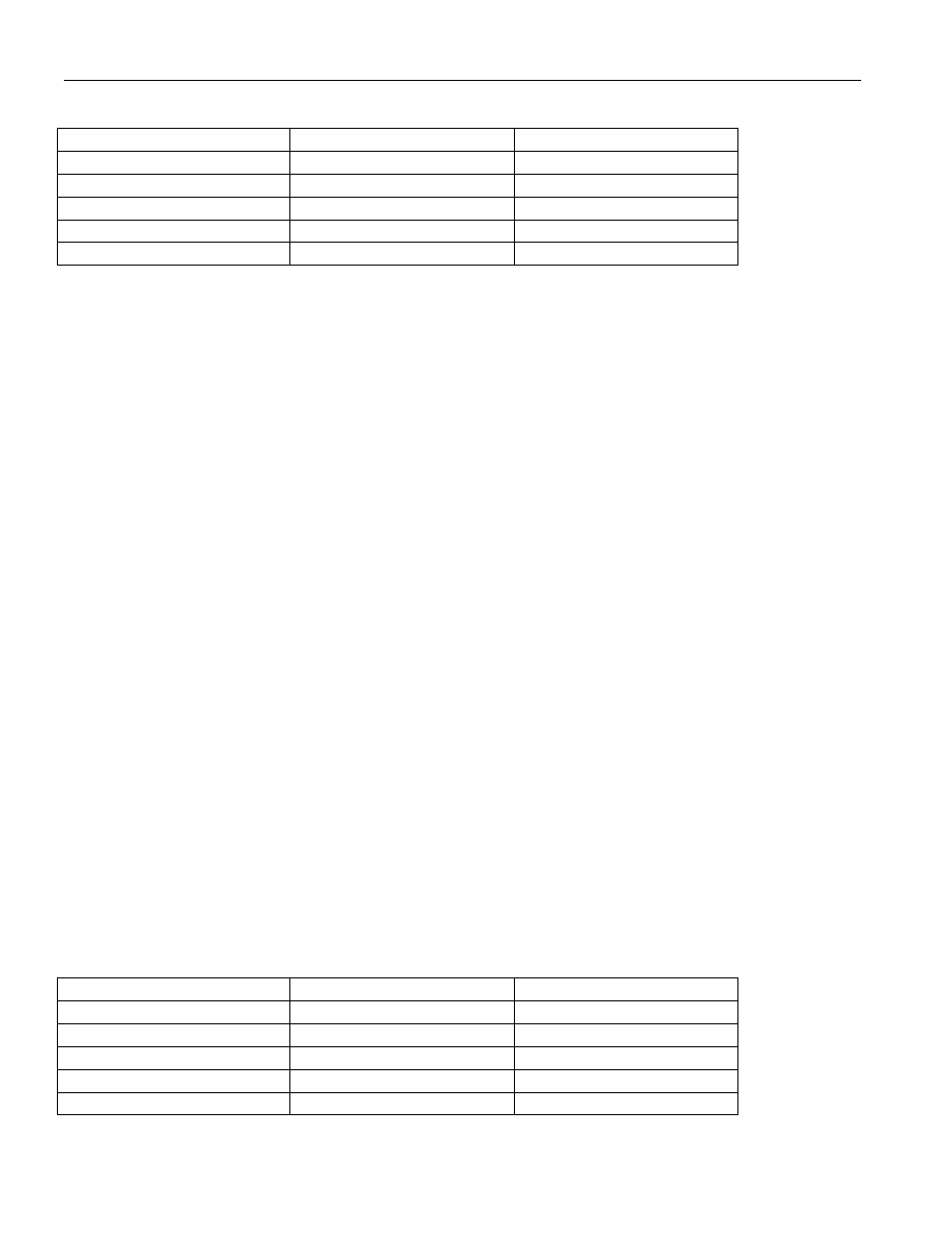

TS SAMPLED EDGE Table 2.2B

Normal TC Clock Mode

Inverted TC Clock Mode

0 TC Clock Early Mode

falling edge

rising edge

1/2 TC Clock Early Mode

rising edge

falling edge

1 TC Clock Early Mode

falling edge

rising edge

2 TC Clock Early Mode

falling edge

rising edge