Rainbow Electronics DS3134 User Manual

Page 152

DS3134

152 of 203

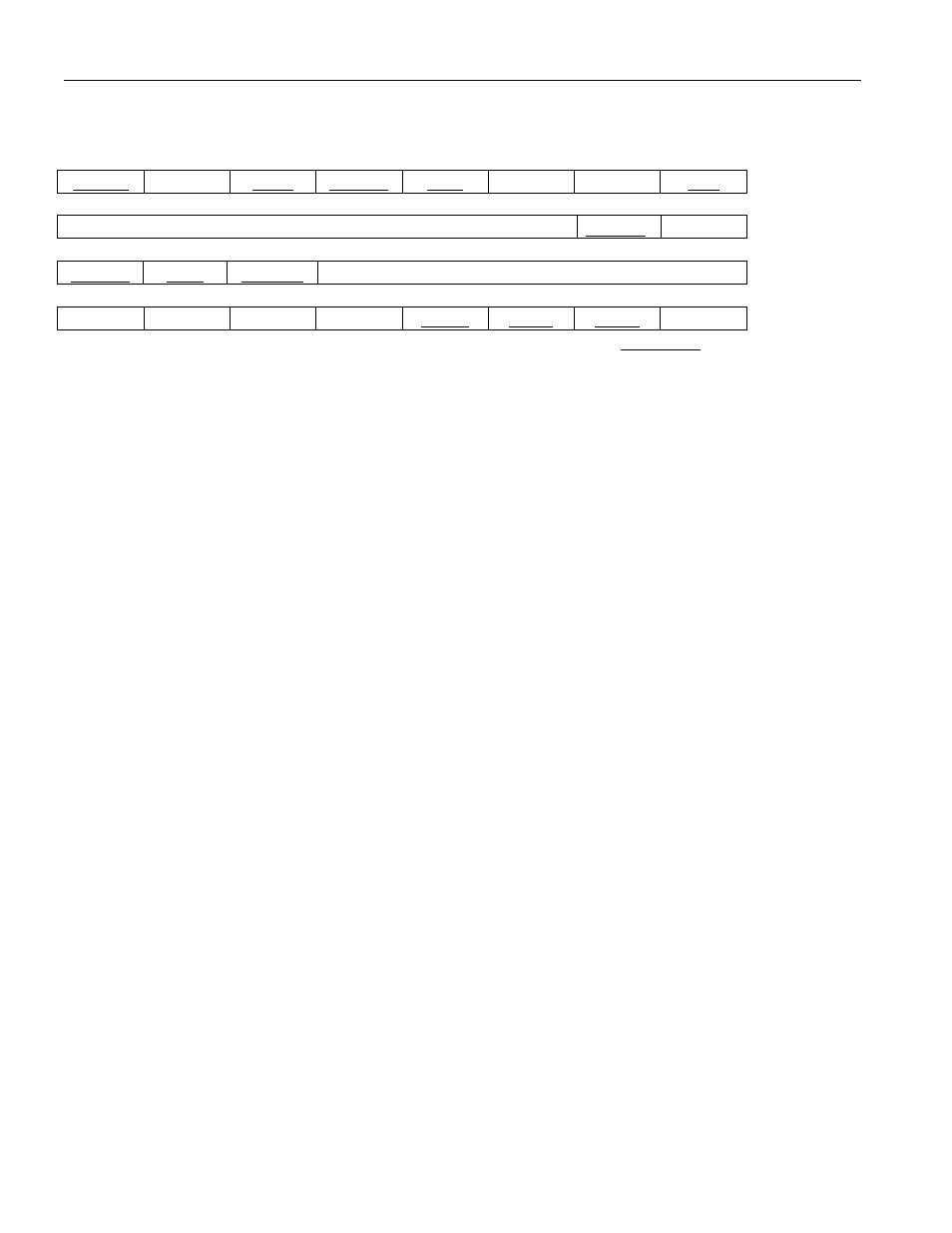

Register Name:

PCMD0

Register Description: PCI Command / Status Register 0

Register Address:

0x004

lsb

STEPC

PARC

VGA

MWEN

SCC

MASC

MSC

IOC

Reserved (Read Only / set to all zeros)

FBBEN

PSEC

FBBCT

UDF

66 MHz

Reserved (Read Only / set to all zeros)

msb

PPE

PSE

MABT

TABTM

TABT

DTS1

DTS0

PARR

Note : Read only bits in the PCMD0 register are indicated above by being underlined. All other bits are

read-write.

The lower word (bits 0 to 15) of the PCMD0 register is the Command portion and is used for control of

the PCI bus. When all bits in the lower word are set to zero, then the device is logically disconnected

from the bus for all accesses except for accesses to the configuration registers. The upper word (bits 16 to

31) is the Status portion and it is used for status information. Reads to the Status portion behave normally

but writes are unique in that bits can be reset (i.e. forced to zero) but not set (i.e. forced to one). A bit in

the Status portion will be reset when a one is written to that bit position. Bit positions that have a zero

written to them will not be reset.

COMMAND BITS

Bit 0 / I/O Space Control (IOC). This read only bit is forced to zero by the device to indicate that it

does not respond to I/O Space accesses.

Bit 1 / Memory Space Control (MSC). This read/write bit controls whether or not the device will

respond to accesses by the PCI bus to the memory space (which is the internal device configuration

registers). When this bit is set to zero, the device will ignore accesses attempted to the internal

configuration registers and when set to one; the device will allow accesses to the internal configuration

registers. This bit should be set to zero when the Local Bus is operated in the Configuration Mode. This

bit is force to zero when a hardware reset is initiated via the PRST* pin.

0 = ignore accesses to the internal device configuration registers

1 = allow accesses to the internal device configuration registers

Bit 2 / Master Control (MASC). This read/write bit controls whether or not the device can act as a

master on the PCI bus. When this bit is set to zero, the device cannot act as a master and when it is set to

one, the device can act as a bus master. This bit is forced to zero when a hardware reset is initiated via

the PRST* pin.

0 = deny the device from operating as a bus master

1 = allow the device to operate as a bus master

Bit 3 / Special Cycle Control (SCC). This read only bit is forced to zero by the device to indicate that it

cannot decode Special Cycle operations.

Bit 4 / Memory Write & Invalidate Command Enable (MWEN). This read only bit is forced to zero

by the device to indicate that it cannot generate the Memory Write and Invalidate command.