Pci target disconnect figure 9.1g pci target abort, Pci target abort figure 9.1h pci fast back-to-back – Rainbow Electronics DS3134 User Manual

Page 150

DS3134

150 of 203

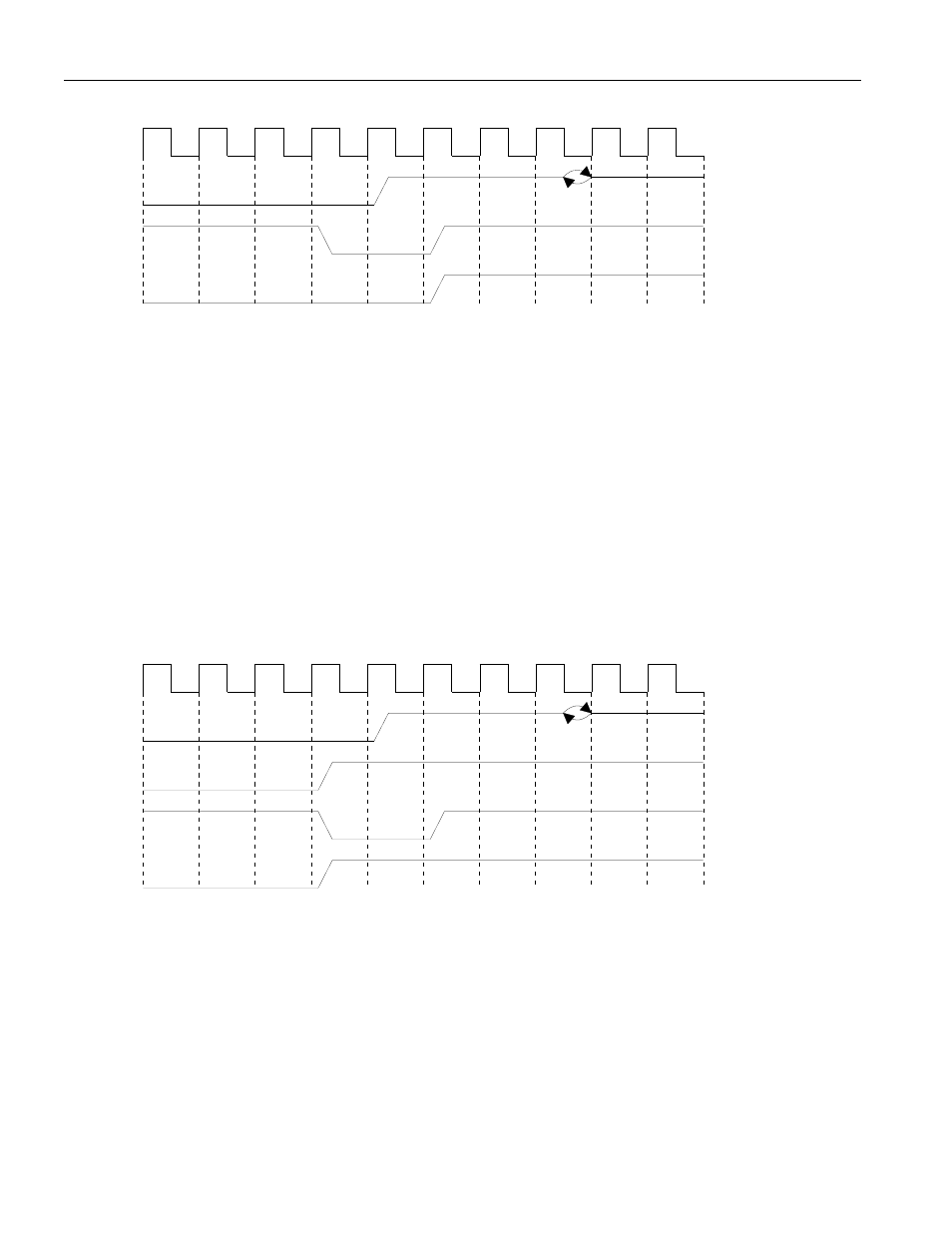

PCI Target Disconnect Figure 9.1G

PCI Target Abort

Targets can also abort the current transaction which means that it does not wish for the initiator to attempt

the request again. No data is transferred in a target abort scenario. A target abort is signaled to the

initiator by the simultaneous assertion of PSTOP* and deassertion of PDEVSEL* (see Figure 9.1H).

When Chateau is a target, it will only issue a target abort when the Host is accessing the Local Bus. This

will occur when the Host attempts a bus transaction with a combination of bytes enables (PCBE*) that is

not supported by the Local Bus. If such a scenario occurs, it will be reported via the Target Abort

Initiated status bit in the PCI Command/Status configuration register (see Section 9.2). See Section 10.1

for details on Local Bus operation. When Chateau is a bus master, if it detects a target abort, then it will

be reported via the Target Abort Detected by Master status bit in the PCI Command/Status configuration

register (see Section 9.2).

PCI Target Abort Figure 9.1H

PCI Fast Back-to-Back

Fast back-to-back transactions are two consecutive bus transactions without the usually required idle

cycle (PFRAME* and PIRDY* deasserted) between them. This can only occur when there is a guarantee

that there will not be any contention on the signal lines. The PCI specification allows two types of fast

back-to-back transactions, those that access the same agent (Type 1) and those that do not (Type 2).

Figure 9.1J shows an example of a fast back-to-back transaction where no idle cycle exists. As a bus

master, Chateau is no capable of performing a Type 2 access. As a target, it can accept both types of fast

back-to-back transactions.

1

2

3

4

5

6

7

8

9

10

PCLK

PFRAME*

PSTOP*

PDEVSEL*

pci_tdis

1

2

3

4

5

6

7

8

9

10

PCLK

PFRAME*

PSTOP*

PDEVSEL*

pci_tabt

PTRDY*