Rainbow Electronics DS3134 User Manual

Page 110

DS3134

110 of 203

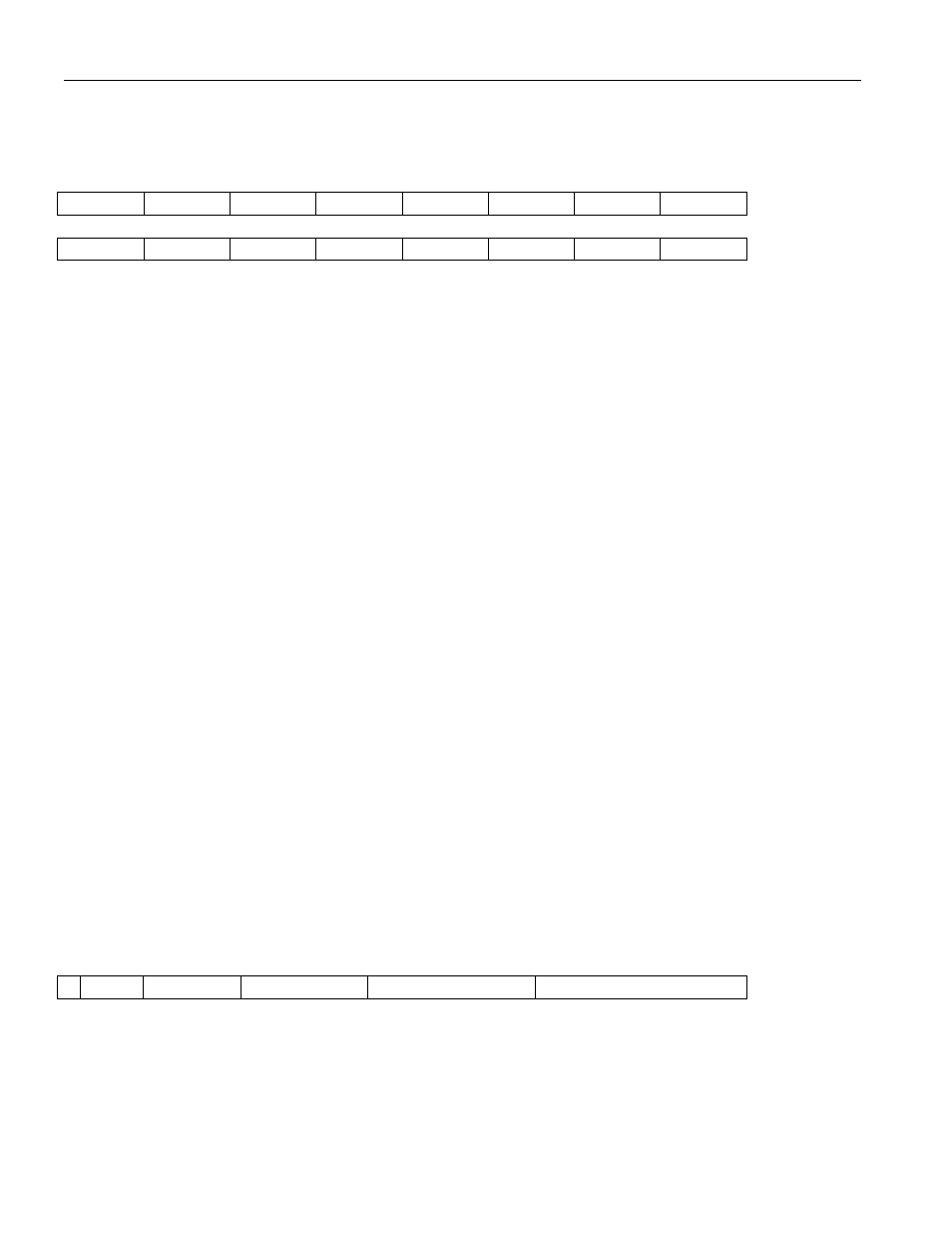

Register Name:

RDMAQ

Register Description: Receive DMA Queues Control

Register Address:

0780h

7

6

5

4

3

2

1

0

n/a

n/a

RDQF

RDQFE

RFQSF

RFQLF

n/a

RFQFE

15

14

13

12

11

10

9

8

n/a

n/a

n/a

n/a

n/a

RDQT2

RDQT1

RDQT0

Note: Bits that are underlined are read only, all other bits are read-write; default value for all bits is 0.

Bit 0 / Receive Free Queue FIFO Enable (RFQFE). To enable the DMA to burst read descriptors from

the Free Queue; this bit must be set to a one. If this bit is set to zero, descriptors will be read one at a

time.

0 = Free Queue Burst Read Disabled

1 = Free Queue Burst Read Enabled

Bit 2 / Receive Free Queue Large Buffer FIFO Flush (RFQLF). When this bit is set to one, the

internal Large Buffer Free Queue FIFO will be flushed (currently loaded Free Queue Descriptors are lost).

This bit must be set to zero for proper operation.

0 = FIFO in normal operation

1 = FIFO is flushed

Bit 3 / Receive Free Queue Small Buffer FIFO Flush (RFQSF). When this bit is set to one, the

internal Small Buffer Free Queue FIFO will be flushed (currently loaded Free Queue Descriptors are lost).

This bit must be set to zero for proper operation.

0 = FIFO in normal operation

1 = FIFO is flushed

Bit 4 / Receive Done Queue FIFO Enable (RDQFE). See Section 8.1.4 for details.

Bit 5 / Receive Done Queue FIFO Flush (RDQF). See Section 8.1.4 for details.

Bits 8 to 10 / Receive Done Queue Status Bit Threshold Setting (RDQT0 to RDQT2). See Section

8.1.4 for details.

8.1.4 DONE QUEUE

The DMA will write to the Receive Done Queue when it has filled a free data buffer with packet data and

has loaded the associated Packet Descriptor with all the necessary information. The descriptor location is

indicated via a 16-bit pointer which the Host will use along with the Receive Descriptor Base Address to

find the exact 32-bit address of the associated Receive Descriptor.

Receive Done Queue Descriptor Figure 8.1.4A

dword 0

V EOF

Status (3)

BUFCNT(3)

HDLC Channel (8)

Descriptor Pointer (16)

Note:

1) Organization of the Done Queue is not affected by the enabling of Big Endian

2) Descriptor Pointer is an index and is not an absolute address.