Rainbow Electronics DS3134 User Manual

Page 39

DS3134

39 of 203

SECTION 4: GENERAL DEVICE CONFIGURATION & STATUS/INTERRUPT

4.1 MASTER RESET & ID REGISTER DESCRIPTION

The Master Reset & ID (MRID) register can be used to globally reset the device. When the RST bit is set

to one, all of the internal registers (except the PCI configuration registers) will be placed into their default

state, which is 0000h. The Host must set the RST bit back to zero before the device can be programmed

for normal operation. The RST bit does not force the PCI outputs to tri-state as does the hardware reset

which is invoked via the PRST* pin. A reset invoked by the PRST* pin will force the RST bit to zero as

well as the rest of the internal configuration registers. See Section 1 for more details on device

initialization.

The upper byte of the MRID register is read only and it can be read by the Host to determine the chip

revision. Contact the factory for specifics on the meaning of the value read from the ID0 to ID7 bits.

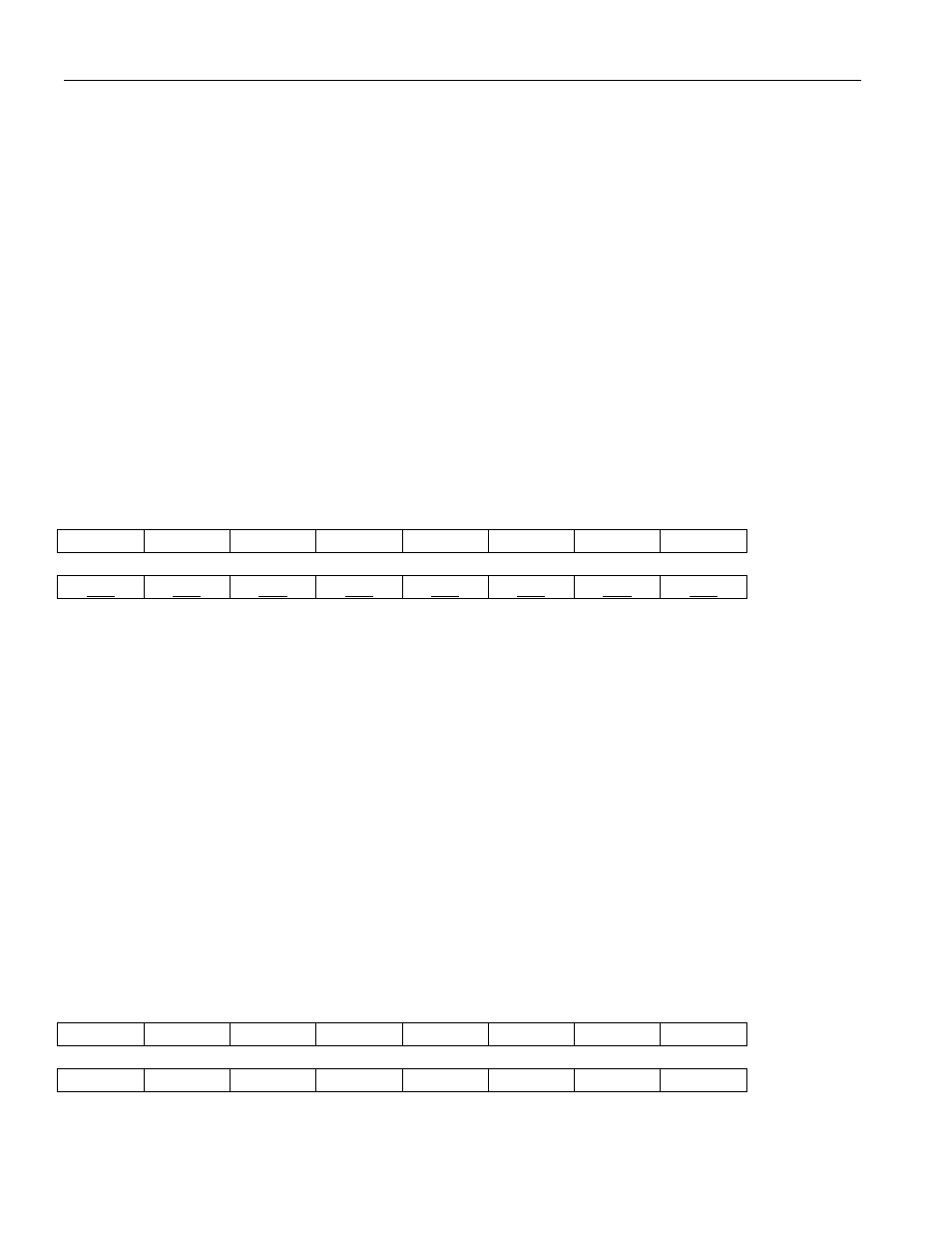

Register Name:

MRID

Register Description: Master Reset and ID Register

Register Address:

0000h

7

6

5

4

3

2

1

0

n/a

n/a

n/a

n/a

n/a

n/a

n/a

RST

15

14

13

12

11

10

9

8

ID7

ID6

ID5

ID4

ID3

ID2

ID1

ID0

Note: Bits that are underlined are read only, all other bits are read-write; default value for all bits is 0.

Bit 0 / Master Software Reset (RST).

0 = normal operation

1 = force all internal registers (except LBBMC) to their default value of 0000h

Bits 8 to 15 / Chip Revision ID Bit 0 to 7 (ID0 to ID7). Read only. Contact the factory for details on

the meaning of the ID bits.

4.2 MASTER CONFIGURATION REGISTER DESCRIPTION

The Master Configuration (MC) register is used by the Host to enable the receive and transmit DMAs as

well as to control their PCI Bus bursting attributes and to select which port the BERT is to be dedicated

to.

Register Name:

MC

Register Description: Master Configuration Register

Register Address:

0010h

7

6

5

4

3

2

1

0

BPS0

PBO

TDT1

TDT0

TDE

RDT1

RDT0

RDE

15

14

13

12

11

10

9

8

TFPC1

TFPC0

RFPC1

RFPC0

BPS4

BPS3

BPS2

BPS1

Note: Bits that are underlined are read only, all other bits are read-write; default value for all bits is 0.