Samsung S3C2440A User Manual

Page 76

S3C2440A RISC MICROPROCESSOR

ARM INSTRUCTION SET

3-19

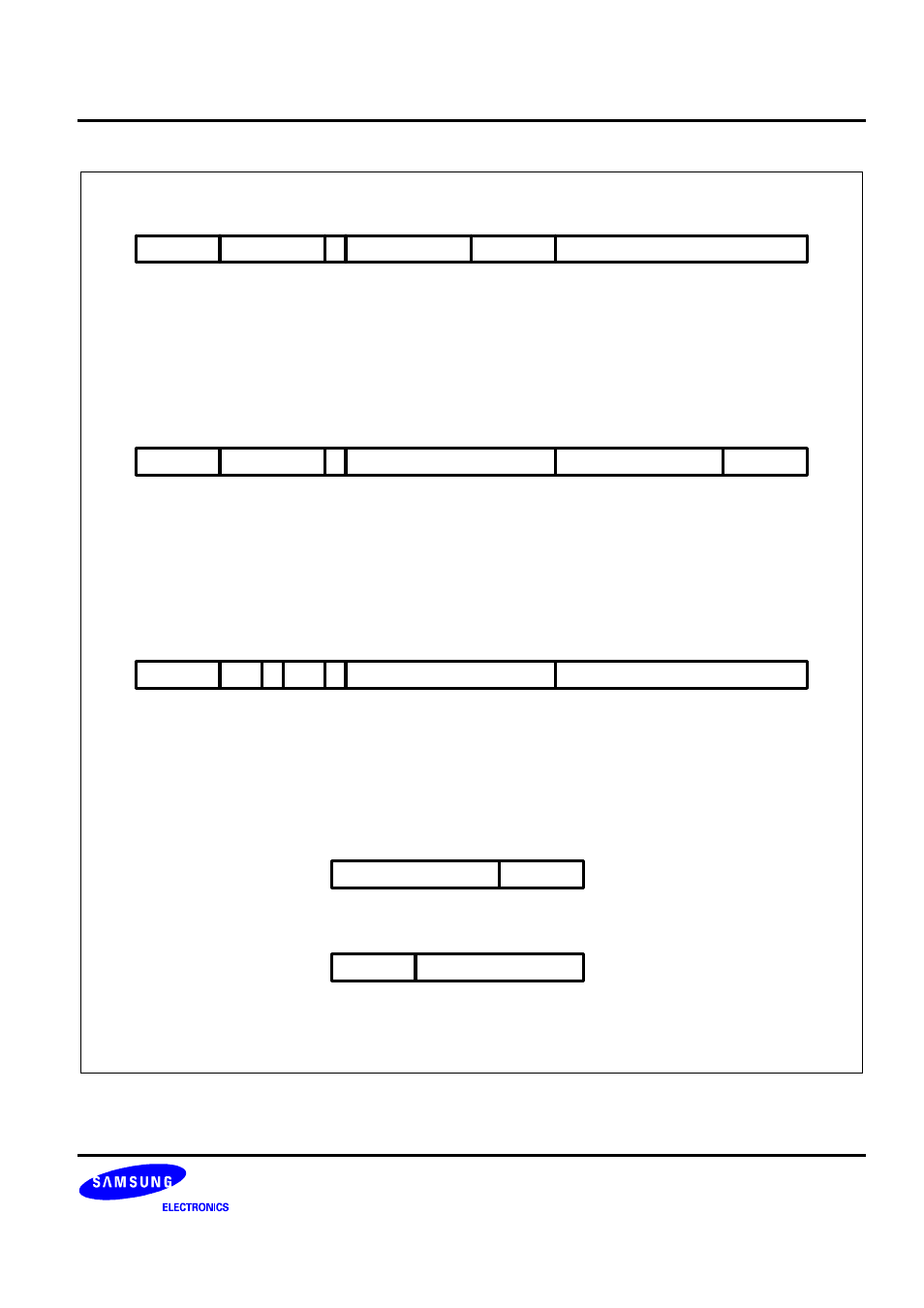

MSR (transfer register contents or immediate value to PSR flag bits only)

Cond

Source operand

Pd

101001111

31

22

27

28

11

12

21

23

I

10

00

26 25 24

0

Cond

00000000

00010

Pd

101001111

31

22

27

28

11

12

21

23

Rm

MSR

(transfer register contents to PSR)

4

3

0

Cond

000000000000

00010

Rd

Ps

001111

31

22

27

15

28

16

11

12

21

23

MRS (transfer PSR contents to a register)

0

[3:0] Source Register

[22] Destination PSR

0 = CPSR

1 = SPSR_

[31:28] Condition Field

[15:12] Destination Register

[22] Source PSR

0 = CPSR

1 = SPSR_

[31:28] Condition Field

[3:0] Source Register

[11:4] Source operand is an immediate value

[7:0] Unsigned 8 bit immediate value

[11:8] Shift applied to Imm

[22] Destination PSR

0 = CPSR

1 = SPSR_

[25] Immediate Operand

0 = Source operand is a register

1 = SPSR_

[11:0] Source Operand

[31:28] Condition Field

00000000

Rm

11

4

3

0

Rotate

Imm

11

0

8

7

Figure 3-11. PSR Transfer

- NC10 (12 pages)

- GT-P7300 (133 pages)

- M6000 (130 pages)

- M60 (201 pages)

- P55 (172 pages)

- Tablet (44 pages)

- Q45c (199 pages)

- Galaxy Tab 8.9 (188 pages)

- X22 (197 pages)

- Q46 (194 pages)

- GT-P7100 (108 pages)

- R71 (196 pages)

- Q71 (191 pages)

- M55 (161 pages)

- GT-P6210 (200 pages)

- V1.3.0 (26 pages)

- Q35 (157 pages)

- 8.9 (176 pages)

- X65 (195 pages)

- Galaxy Tab A3LSGHI987 (146 pages)

- GALAXY Tab SGH-I987 (149 pages)

- Q30 (127 pages)

- NP270E5V (27 pages)

- NP670Z5E (157 pages)

- NP275E5E (135 pages)

- NP270E5GI (134 pages)

- NP535U3C (154 pages)

- NP370R5E (133 pages)

- XE500T1C (117 pages)

- XE500T1C (122 pages)

- NP270E5UE (27 pages)

- NP930X5J-S01US (115 pages)

- NP930X5J-S01US (149 pages)

- NP900X3D-A03US (138 pages)

- NP900X4D-A03US (129 pages)

- NP470R5E-K01UB (120 pages)

- NP470R5E-K01UB (126 pages)

- NP470R5E-K01UB (125 pages)

- NP700Z3C-S01US (156 pages)

- NP355V4C-A01VE (140 pages)

- NP940X3G-S01US (149 pages)

- NP940X3G-S01US (147 pages)

- NP915S3G-K02US (118 pages)

- NP915S3G-K02US (145 pages)