Single data swap (swp) – Samsung S3C2440A User Manual

Page 104

S3C2440A RISC MICROPROCESSOR

ARM INSTRUCTION SET

3-47

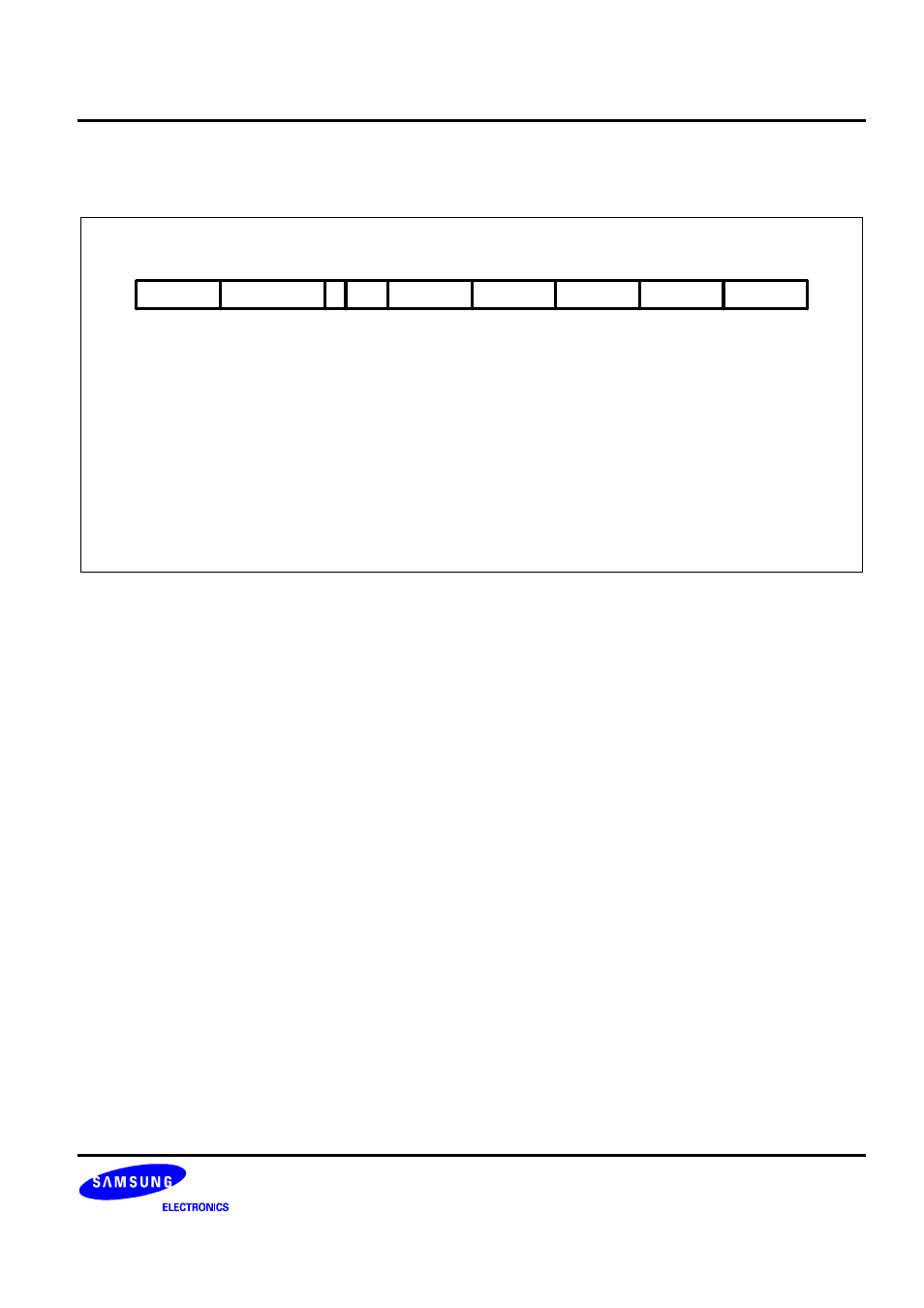

SINGLE DATA SWAP (SWP)

31

19

15

Cond

28

16

11

12

21

23

B

20

00

Rn

Rd

[3:0] Source Register

[15:12] Destination Register

[19:16] Base Register

[22] Byte/Word Bit

0 = Swap word quantity

1 = Swap word quantity

[31:28] Condition Field

22

00010

0000

Rm

1001

27

8 7

4 3

0

Figure 3-23. Swap Instruction

The instruction is only executed if the condition is true. The various conditions are defined in Table 3-2. The

instruction encoding is shown in Figure 3-23.

The data swap instruction is used to swap a byte or word quantity between a register and external memory. This

instruction is implemented as a memory read followed by a memory write which are “locked” together (the

processor cannot be interrupted until both operations have completed, and the memory manager is warned to treat

them as inseparable). This class of instruction is particularly useful for implementing software semaphores.

The swap address is determined by the contents of the base register (Rn). The processor first reads the contents

of the swap address. Then it writes the contents of the source register (Rm) to the swap address, and stores the

old memory contents in the destination register (Rd). The same register may be specified as both the source and

destination.

The LOCK output goes HIGH for the duration of the read and write operations to signal to the external memory

manager that they are locked together, and should be allowed to complete without interruption. This is important in

multi-processor systems where the swap instruction is the only indivisible instruction which may be used to

implement semaphores; control of the memory must not be removed from a processor while it is performing a

locked operation.

BYTES AND WORDS

This instruction class may be used to swap a byte (B=1) or a word (B=0) between an ARM920T register and

memory. The SWP instruction is implemented as a LDR followed by a STR and the action of these is as described

in the section on single data transfers. In particular, the description of Big and Little Endian configuration applies to

the SWP instruction.