Samsung S3C2440A User Manual

Page 270

I/O PORTS

S3C2440A RISC MICROPROCESSOR

9-24

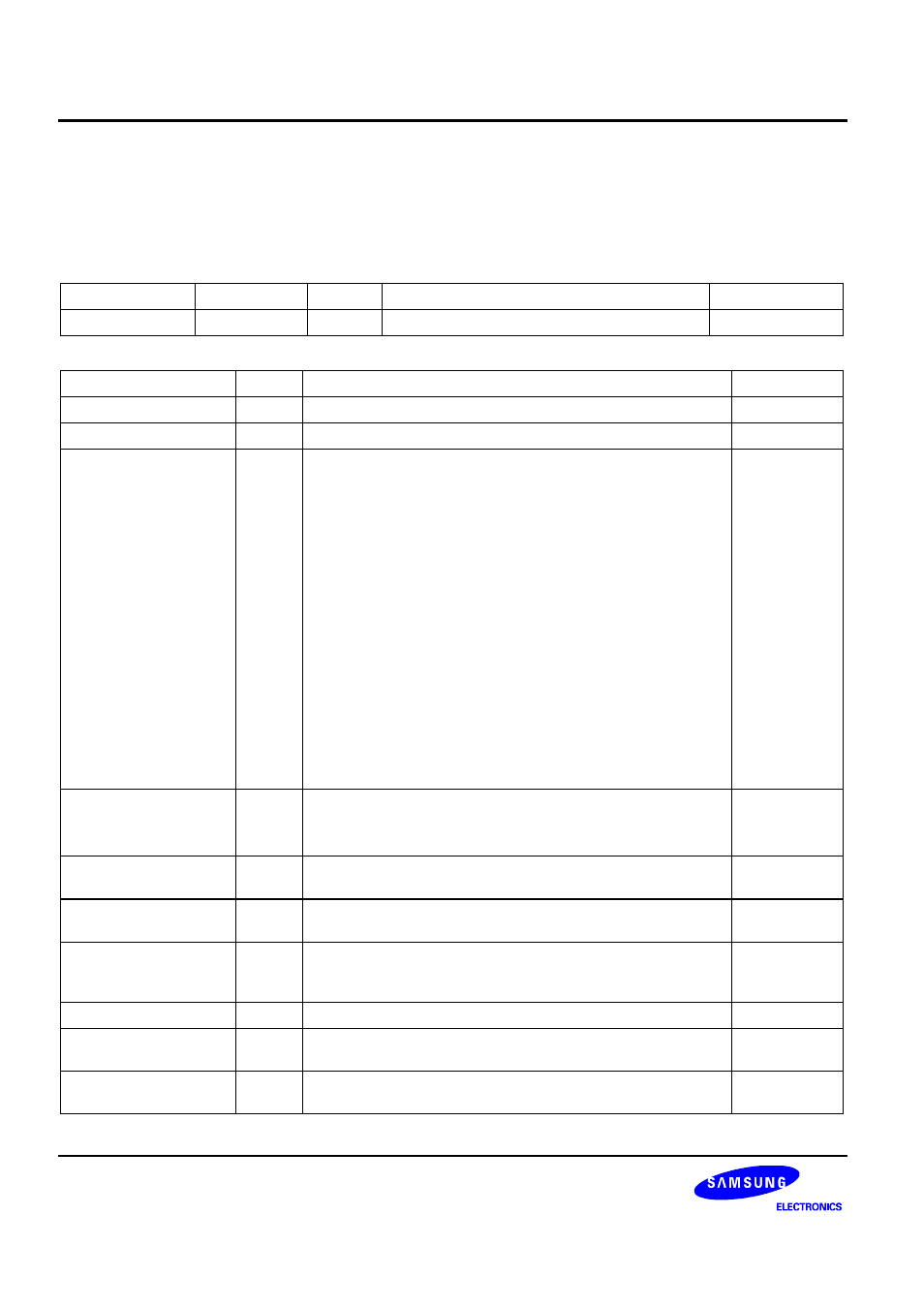

MISCELLANEOUS control register(MISCCR)

In Sleep mode, the data bus(D[31:0] or D[15:0] can be set as Hi-Z and Output ‘0’ state. But, because of the

characteristics of IO pad, the data bus pull-up resisters have to be turned on or off to reduce the power

consumption. D[31:0] pin pull-up resisters can be controlled by MISCCR register.

Pads related USB are controlled by this register for USB host, or for USB device.

Register Address

R/W

Description

Reset

Value

MISCCR

0x56000080

R/W

Miscellaneous control register

0x10020

MISCCR Bit

Description

Reset

Value

Reserved [24]

Reserve to 0.

0

Reserved [23]

Reserve to 0.

0

BATT_FUNC [22:20]

Battery fault function selection.

0XX: In nBATT_FLT=0, The system will be in reset status.

After reset, Change this bit to other values, this bit is only for

preventing from booting in Battery fault status.

10X: In sleep mode status, when nBATT_FLT=0, the system

will wake-up.

In normal mode, when nBATT_FLT=0, the Battery fault

interrupt will occur.

110: In sleep mode status, during nBATT_FLT=0, the

system will ignore all the wake-up events(the system will not

wake-up by wake-up source).

In normal mode, nBATT_FLT signal cannot affect the

system.

111: nBATT_FLT function disable.

000

OFFREFRESH [19]

0: Self refresh retain disable 1: Self refresh retain enable

When 1, After wake-up from sleep, The self-refresh will be

retained.

0

nEN_SCLK1 [18]

SCLK1 output enable

0: SCLK1 = SCLK

1: SCLK1 = 0

0

nEN_SCLK0 [17]

SCLK0 output enable

0: SCLK0 = SCLK

1: SCLK 0 = 0

0

nRSTCON [16]

nRSTOUT signal manual control

0: nRSTOUT signal level will be low(‘0’)

1: nRSTOUT singal level will be high(‘1’)

1

Reserved [15:14]

- 00

SEL_SUSPND1 [13]

USB Port 1 Suspend mode

0 = normal mode

1= suspend mode

0

SEL_SUSPND0 [12]

USB Port 0 Suspend mode

0 = normal mode

1= suspend mode

0