Samsung S3C2440A User Manual

Page 346

USB DEVICE

S3C2440A RISC MICROPROCESSOR

13-18

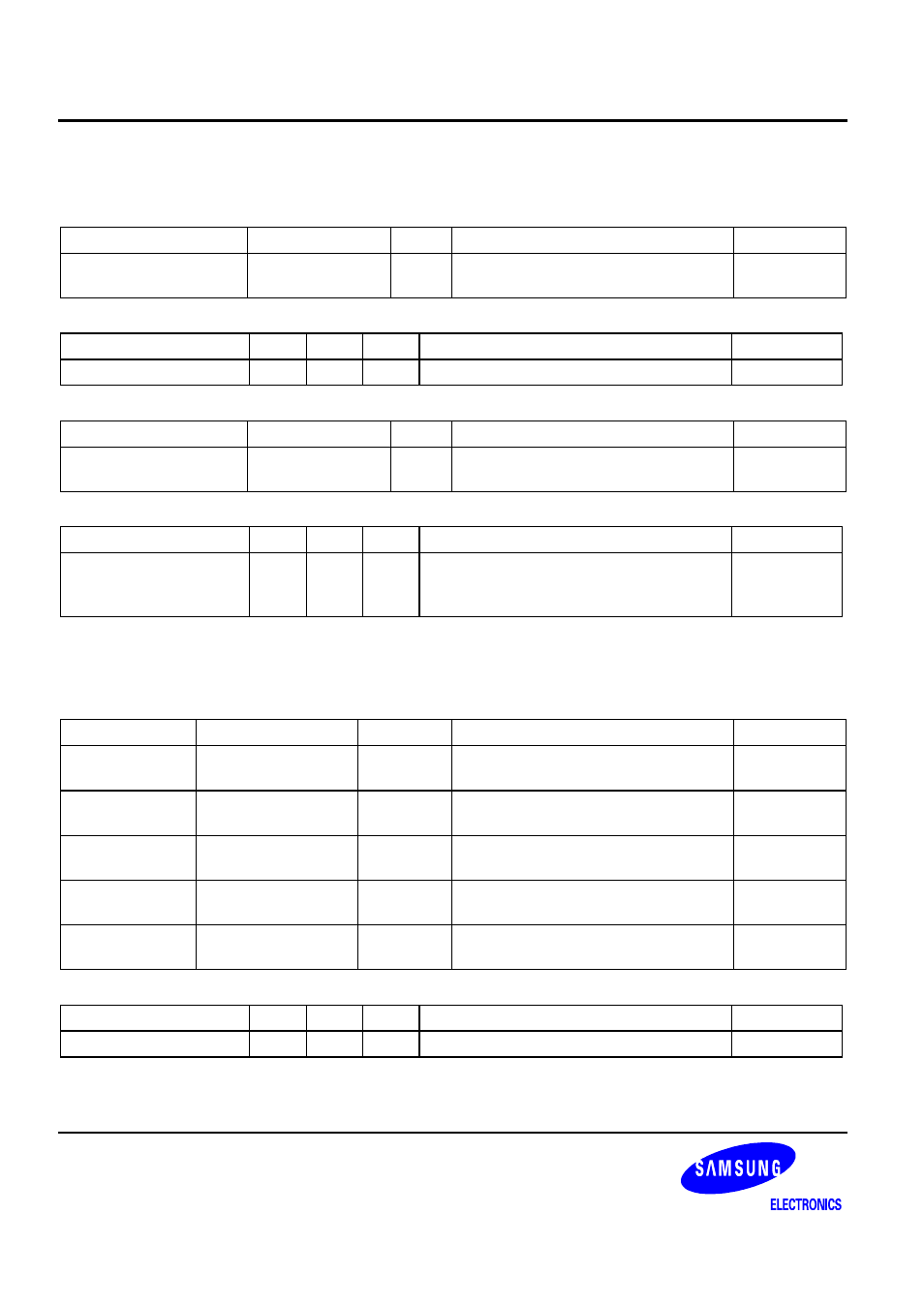

END POINT OUT WRITE COUNT REGISTER (OUT_FIFO_CNT1_REG/OUT_FIFO_CNT2_REG)

These registers maintain the number of bytes in the packet as the number is unloaded by the MCU.

Register Address

R/W Description Reset

Value

OUT_FIFO_CNT1_REG 0x52000198(L)

0x5200019B(B)

R

(byte)

End Point out write count register1

0x00

OUT_FIFO_CNT1_REG Bit MCU USB

Description

Initial

State

OUT_CNT_LOW

[7:0]

R

W

Lower byte of write count

0x00

Register Address

R/W Description Reset

Value

OUT_FIFO_CNT2_REG 0x5200019C(L)

0x5200019F(B)

R

(byte)

End Point out write count register2

0x00

OUT_FIFO_CNT2_REG Bit MCU USB

Description

Initial

State

OUT_CNT_HIGH

[7:0]

R

W

Higher byte of write count. The

OUT_CNT_HIGH may be always 0

normally.

0x00

END POINT FIFO REGISTER (EPN_FIFO_REG)

The EPn_FIFO_REG enables the MCU to access to the EPn FIFO.

Register Address R/W

Description

Reset

Value

EP0_FIFO 0x520001C0(L)

0x520001C3 (B)

R/W

(byte)

End Point0 FIFO register

0xXX

EP1_FIFO 0x520001C4(L)

0x520001C7(B)

R/W

(byte)

End Point1 FIFO register

0xXX

EP2_FIFO 0x520001C8(L)

0x520001CB(B)

R/W

(byte)

End Point2 FIFO register

0xXX

EP3_FIFO 0x520001CC(L)

0x520001CF(B)

R/W

(byte)

End Point3 FIFO register

0xXX

EP4_FIFO 0x520001D0(L)

0x520001D3(B)

R/W

(byte)

End Point4 FIFO register

0xXX

EPn_FIFO Bit

MCU

USB

Description

Initial

State

FIFO_DATA

[7:0]

R/W

R/W

FIFO data value

0xXX