Samsung S3C2440A User Manual

Page 182

S3C2440A RISC MICROPROCESSOR

MEMORY CONTROLLER

DEC.13, 2002

5-17

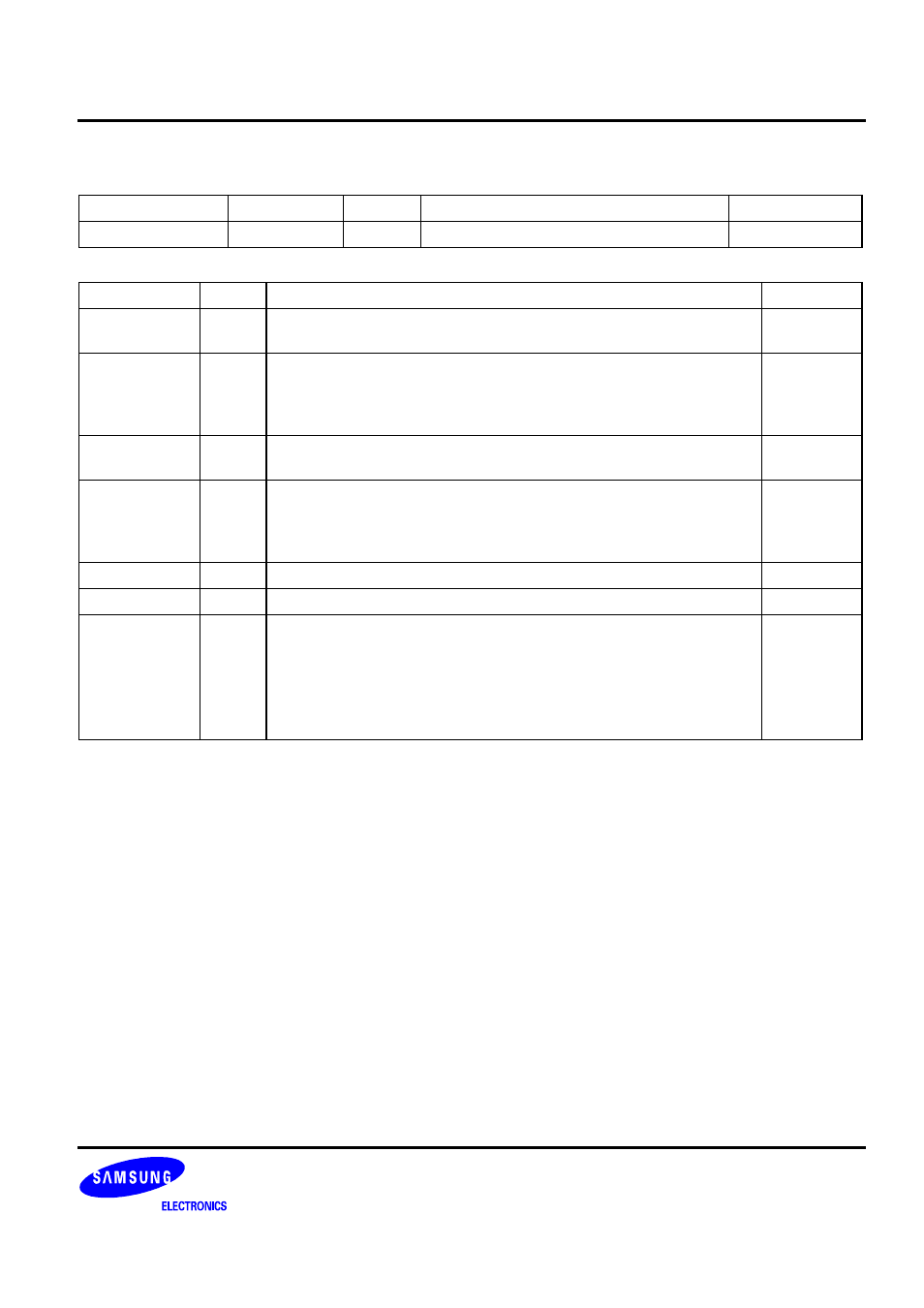

REFRESH CONTROL REGISTER

Register Address

R/W

Description

Reset

Value

REFRESH

0x48000024

R/W

SDRAM refresh control register

0xac0000

REFRESH Bit

Description

Initial

State

REFEN

[23]

SDRAM Refresh Enable

0 = Disable 1 = Enable (self or CBR/auto refresh)

1

TREFMD

[22]

SDRAM Refresh Mode

0 = CBR/Auto Refresh 1 = Self Refresh

In self-refresh time, the SDRAM control signals are driven to the

appropriate level.

0

Trp

[21:20] SDRAM RAS pre-charge Time

00 = 2 clocks 01 = 3 clocks 10 = 4 clocks 11 = Not support

10

Tsrc

[19:18] SDRAM Semi Row cycle time

00 = 4 clocks 01 = 5 clocks 10 = 6 clocks 11 = 7 clocks

SDRAM Row cycle time: Trc=Tsrc+Trp

If Trp=3clocks & Tsrc=7clocks, Trc=3+7=10clocks.

11

Reserved [17:16]

Not

used

00

Reserved [15:11]

Not

used

0000

Refresh

Counter

[10:0]

SDRAM refresh count value. Refer to chapter 6 SDRAM refresh

controller bus priority section.

Refresh period = (2

11

-refresh_count+1)/HCLK

Ex) If refresh period is 7.8 us and HCLK is 100 MHz,

the refresh count is as follows:

Refresh count = 2

11

+ 1 - 100x7.8 = 1269

0