Format 16: conditional branch – Samsung S3C2440A User Manual

Page 155

THUMB INSTRUCTION SET

S3C2440A RISC MICROPROCESSOR

4-34

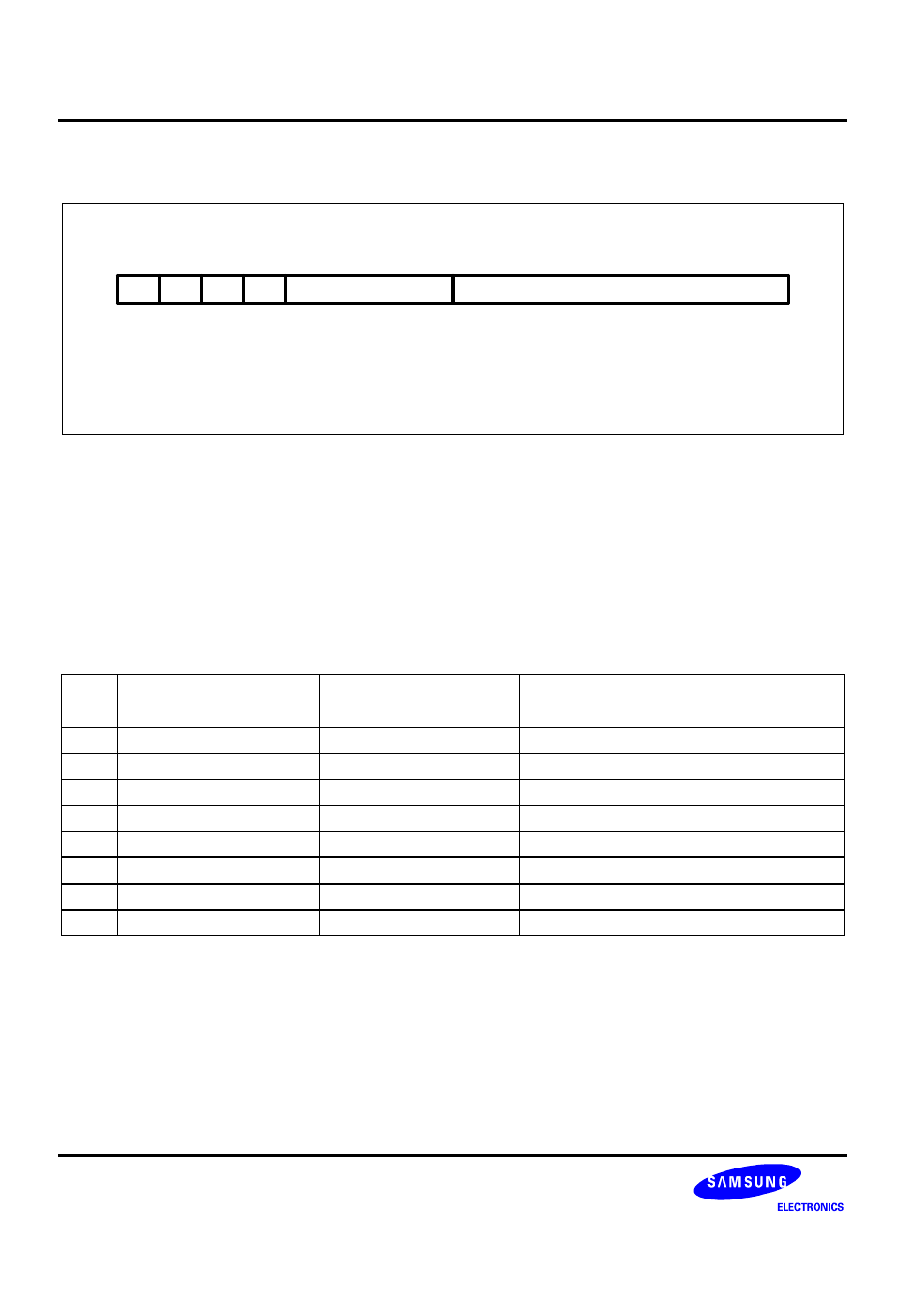

FORMAT 16: CONDITIONAL BRANCH

[7:0] 8-bit Signed Immediate

[11:8] Condition

15

0

1

14

1

0

13

12

11

SOffset 8

1

7

8

Cond

Figure 4-17. Format 16

OPERATION

The instructions in this group all perform a conditional Branch depending on the state of the CPSR condition

codes. The branch offset must take account of the prefetch operation, which causes the PC to be 1 word (4 bytes)

ahead of the current instruction.

The THUMB assembler syntax is shown in the following table.

Table 4-17. The Conditional Branch Instructions

L

THUMB assembler

ARM equivalent

Description

0000 BEQ label

BEQ label

Branch if Z set (equal)

0001 BNE

label

BNE label

Branch if Z clear (not equal)

0010 BCS

label

BCS label

Branch if C set (unsigned higher or same)

0011 BCC

label

BCC label

Branch if C clear (unsigned lower)

0100 BMI

label

BMI label

Branch if N set (negative)

0101 BPL

label

BPL label

Branch if N clear (positive or zero)

0110 BVS

label

BVS label

Branch if V set (overflow)

0111 BVC

label

BVC label

Branch if V clear (no overflow)

1000 BHI

label

BHI label

Branch if C set and Z clear (unsigned higher)