Samsung S3C2440A User Manual

Page 175

MEMORY CONTROLLER

S3C2440A RISC MICROPROCESSOR

5-10

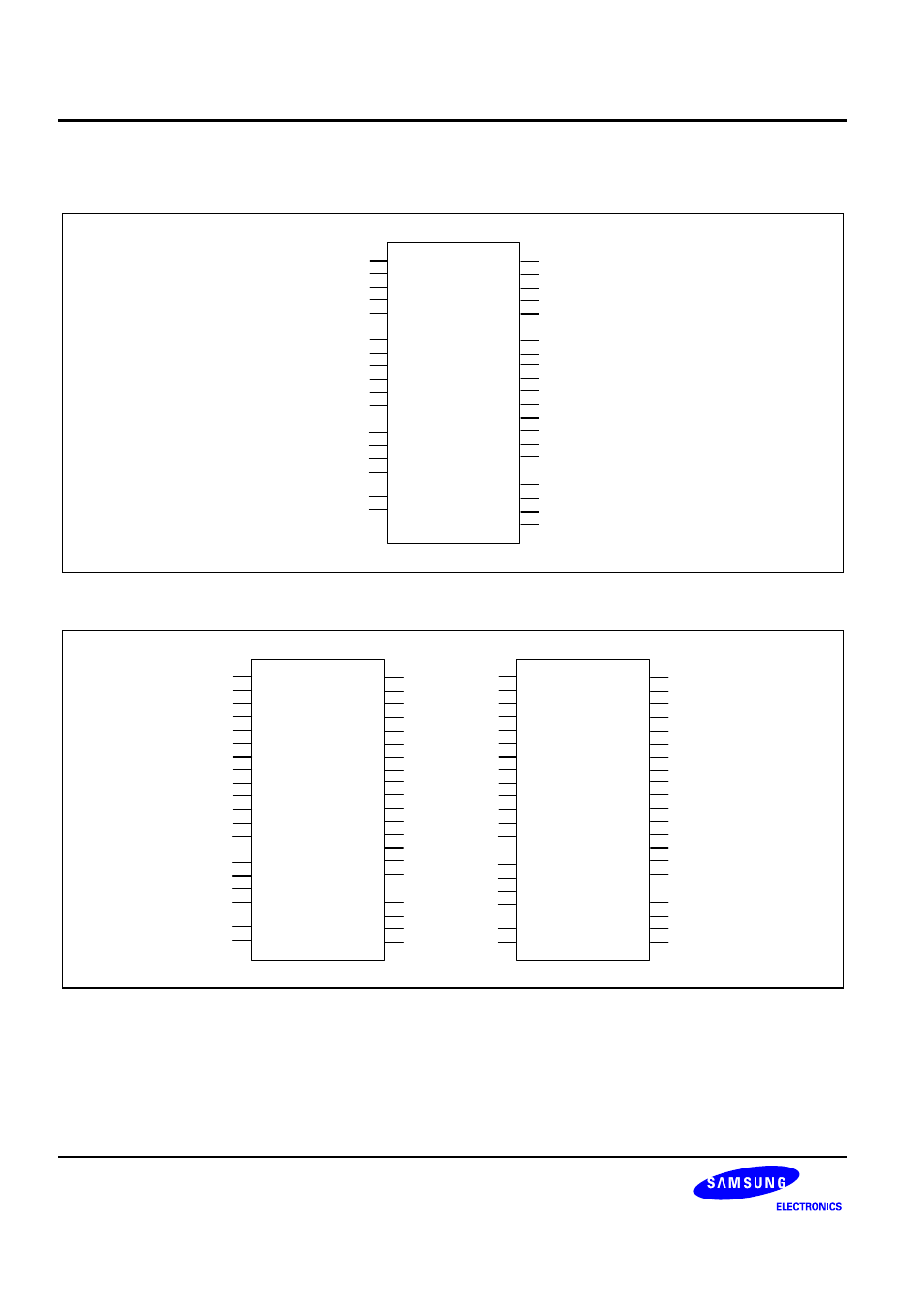

SDRAM Memory Interface Examples

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

BA0

BA1

LDQM

UDQM

A21

A22

DQM0

DQM1

SCKE

SCLK

SCKE

SCLK

nSCS0

nSRAS

nSCAS

nWE

nSCS

nSRAS

nSCAS

nWE

Figure 5-10. Memory Interface with 16-bit SDRAM (4Mx16, 4banks)

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

BA0

BA1

LDQM

UDQM

A24

A25

DQM0

DQM1

SCKE

SCLK

SCKE

SCLK

nSCS0

nSRAS

nSCAS

nWE

nSCS

nSRAS

nSCAS

nWE

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

BA0

BA1

LDQM

UDQM

A24

A25

DQM2

DQM3

SCKE

SCLK

SCKE

SCLK

nSCS0

nSRAS

nSCAS

nWE

nSCS

nSRAS

nSCAS

nWE

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

Figure 5-11. Memory Interface with 16-bit SDRAM (4Mx16x4Bank * 2ea)

Note

Refer to Table 5-2 for the Bank Address configurations of SDRAM.