Samsung S3C2440A User Manual

Page 156

S3C2440A RISC MICROPROCESSOR

THUMB INSTRUCTION SET

4-35

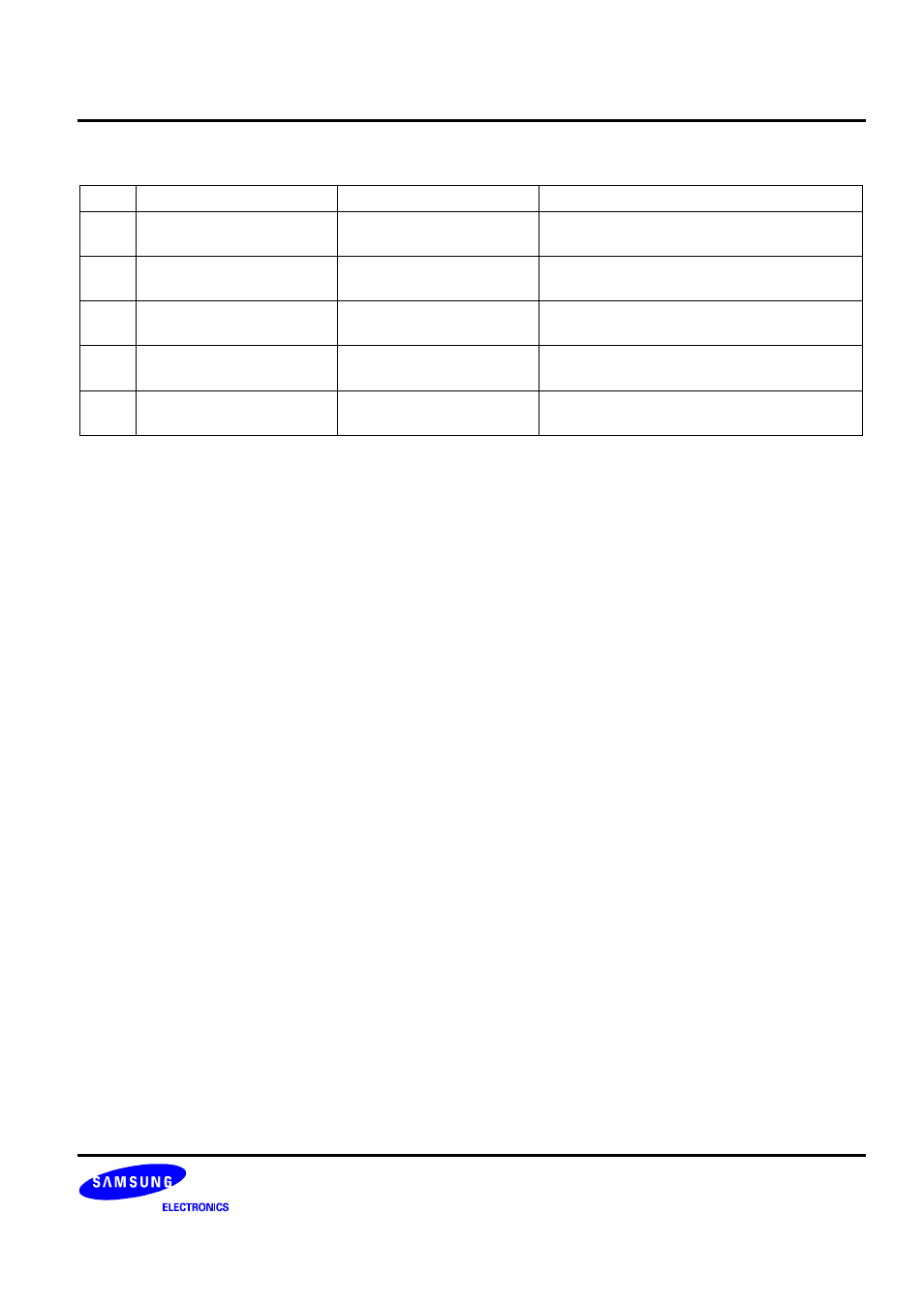

Table 4-17. The Conditional Branch Instructions (Continued)

L

THUMB assembler

ARM equivalent

Description

1001 BLS label

BLS label

Branch if C clear or Z set (unsigned lower or

same)

1010 BGE

label

BGE label

Branch if N set and V set, or N clear and V

clear (greater or equal)

1011 BLT

label

BLT label

Branch if N set and V clear, or N clear and V

set (less than)

1100 BGT

label

BGT label

Branch if Z clear, and either N set and V set

or N clear and V clear (greater than)

1101 BLE

label

BLE label

Branch if Z set, or N set and V clear, or N

clear and V set (less than or equal)

NOTES

1. While label specifies a full 9-bit two's complement address, this must always be halfword-aligned (ie with bit 0 set to 0)

since the assembler actually places label >> 1 in field SOffset8.

2. Cond = 1110 is undefined, and should not be used.

Cond = 1111 creates the SWI instruction: see.

INSTRUCTION CYCLE TIMES

All instructions in this format have an equivalent ARM instruction as shown in Table 3-1. The instruction cycle

times for the THUMB instruction are identical to that of the equivalent ARM instruction.

EXAMPLES

CMP R0, #45

; Branch to over-if R0 > 45.

BGT over

; Note that the THUMB opcode will contain the

number of halfwords to offset.

over

; Must be halfword aligned.