Samsung S3C2440A User Manual

Page 228

S3C2440A RISC MICROPROCESSOR

CLOCK & POWER MANAGEMENT

7

-21

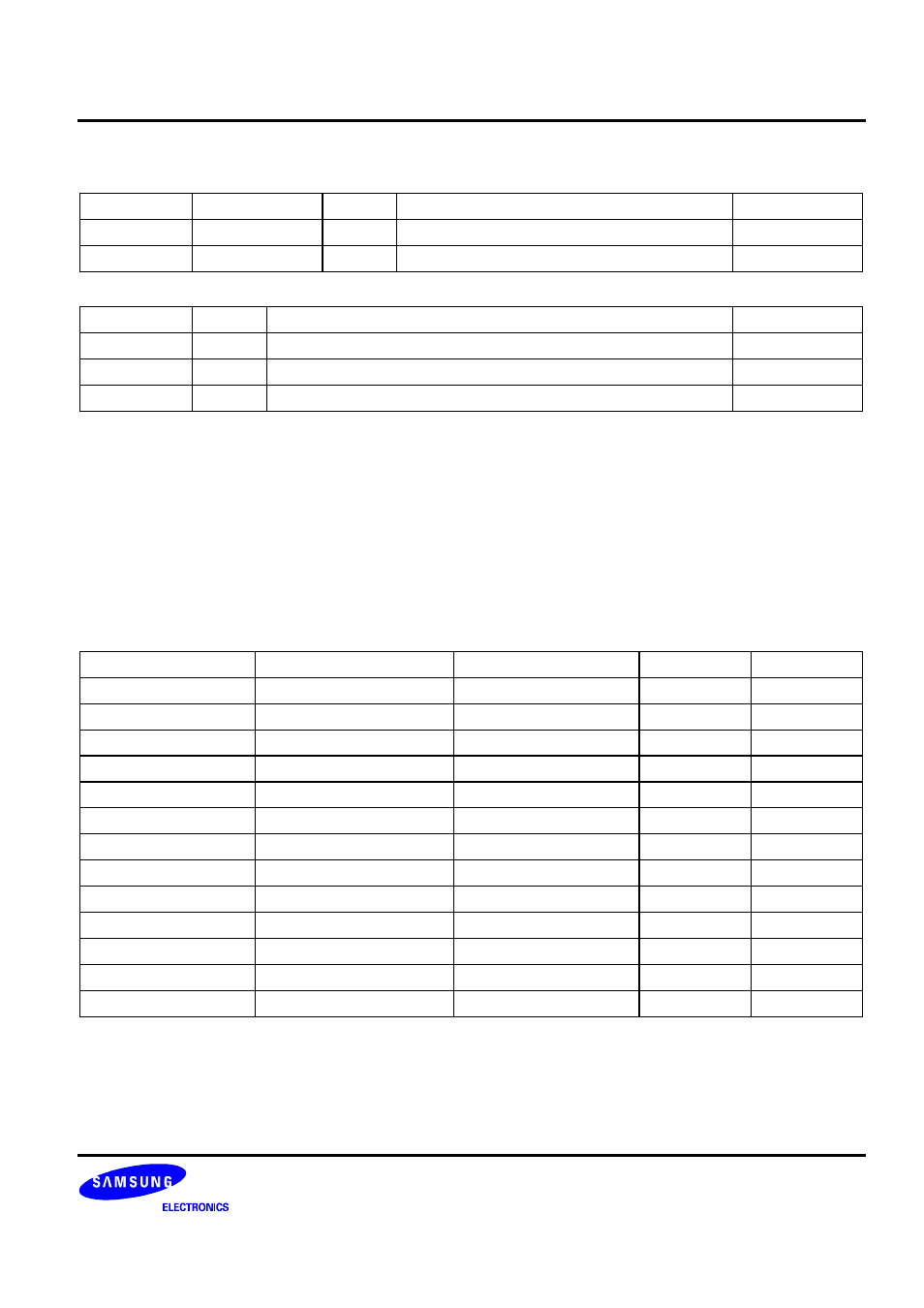

PLL CONTROL REGISTER (MPLLCON & UPLLCON)

Register Address R/W

Description

Reset

Value

MPLLCON

0x4C000004

R/W

MPLL configuration register

0x00096030

UPLLCON

0x4C000008

R/W

UPLL configuration register

0x0004d030

PLLCON Bit

Description

Initial

State

MDIV

[19:12]

Main divider control

0x96 / 0x4d

PDIV

[9:4]

Pre-divider control

0x03 / 0x03

SDIV

[1:0]

Post divider control

0x0 / 0x0

NOTE

When you set MPLL&UPLL values, you have to set the UPLL value first and then the MPLL value. (Needs intervals

approximately 7 NOP)

PLL VALUE SELECTION TABLE

It is not easy to find a proper PLL value. So, we recommend referring to the following PLL value recommendation

table.

Input Frequency

Output Frequency

MDIV

PDIV

SDIV

12.0000MHz

48.00 MHz

(Note)

56(0X38) 2 2

12.0000MHz

96.00 MHz

(Note)

56(0x38) 2 1

12.0000MHz

271.50 MHz

173(0xad)

2

2

12.0000MHz

304.00 MHz

68(0x44)

1

1

12.0000MHz

405.00 MHz

127(0x7f)

2

1

12.0000MHz

532.00 MHz

125(0x7d)

1

1

16.9344MHz

47.98 MHz

(Note)

60(0x3c) 4 2

16.9344MHz

95.96 MHz

(Note)

60(0x3c) 4 1

16.9344MHz

266.72

MHZ

118(0x76) 2

2

16.9344MHz

296.35

MHZ

97(0x61) 1

2

16.9344MHz 399.65

MHz 110(0x6e) 3 1

16.9344MHz 530.61

MHz

86(0x56) 1 1

16.9344MHz 533.43

MHz 118(0x76) 1 1

NOTE

The 48.00MHz and 96MHz output is used for UPLLCON register.