The condition field – Samsung S3C2440A User Manual

Page 61

ARM INSTRUCTION SET

S3C2440A RISC MICROPROCESSOR

3-4

THE CONDITION FIELD

In ARM state, all instructions are conditionally executed according to the state of the CPSR condition codes and

the instruction's condition field. This field (bits 31:28) determines the circumstances under which an instruction is to

be executed. If the state of the C, N, Z and V flags fulfils the conditions encoded by the field, the instruction is

executed, otherwise it is ignored.

There are sixteen possible conditions, each represented by a two-character suffix that can be appended to the

instruction's mnemonic. For example, a Branch (B in assembly language) becomes BEQ for "Branch if Equal",

which means the Branch will only be taken if the Z flag is set.

In practice, fifteen different conditions may be used: these are listed in Table 3-2. The sixteenth (1111) is reserved,

and must not be used.

In the absence of a suffix, the condition field for most instructions is set to "Always" (suffix AL). This means the

instruction will always be executed regardless of the CPSR condition codes.

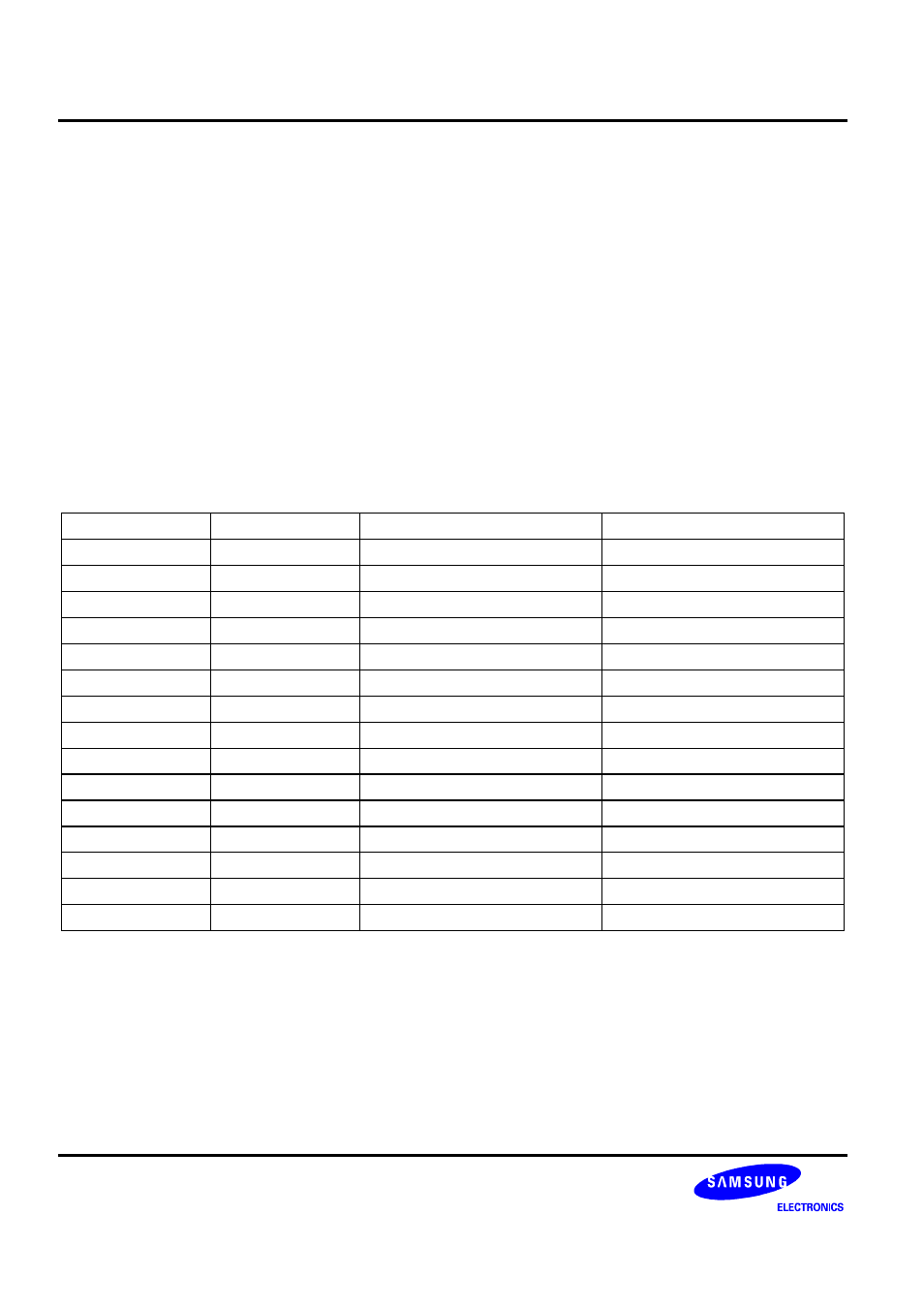

Table 3-2. Condition Code Summary

Code Suffix

Flags

Meaning

0000 EQ

Z

set

equal

0001

NE

Z clear

not equal

0010

CS

C set

unsigned higher or same

0011

CC

C clear

unsigned lower

0100 MI

N

set

negative

0101

PL

N clear

positive or zero

0110 VS

V

set

overflow

0111

VC

V clear

no overflow

1000

HI

C set and Z clear

unsigned higher

1001

LS

C clear or Z set

unsigned lower or same

1010

GE

N equals V

greater or equal

1011

LT

N not equal to V

less than

1100

GT

Z clear AND (N equals V)

greater than

1101

LE

Z set OR (N not equal to V)

less than or equal

1110 AL

(ignored)

always