Camera interface special registers – Samsung S3C2440A User Manual

Page 488

S3C2440A RISC MICROPROCESSOR

CAMERA INTERFACE

23-10

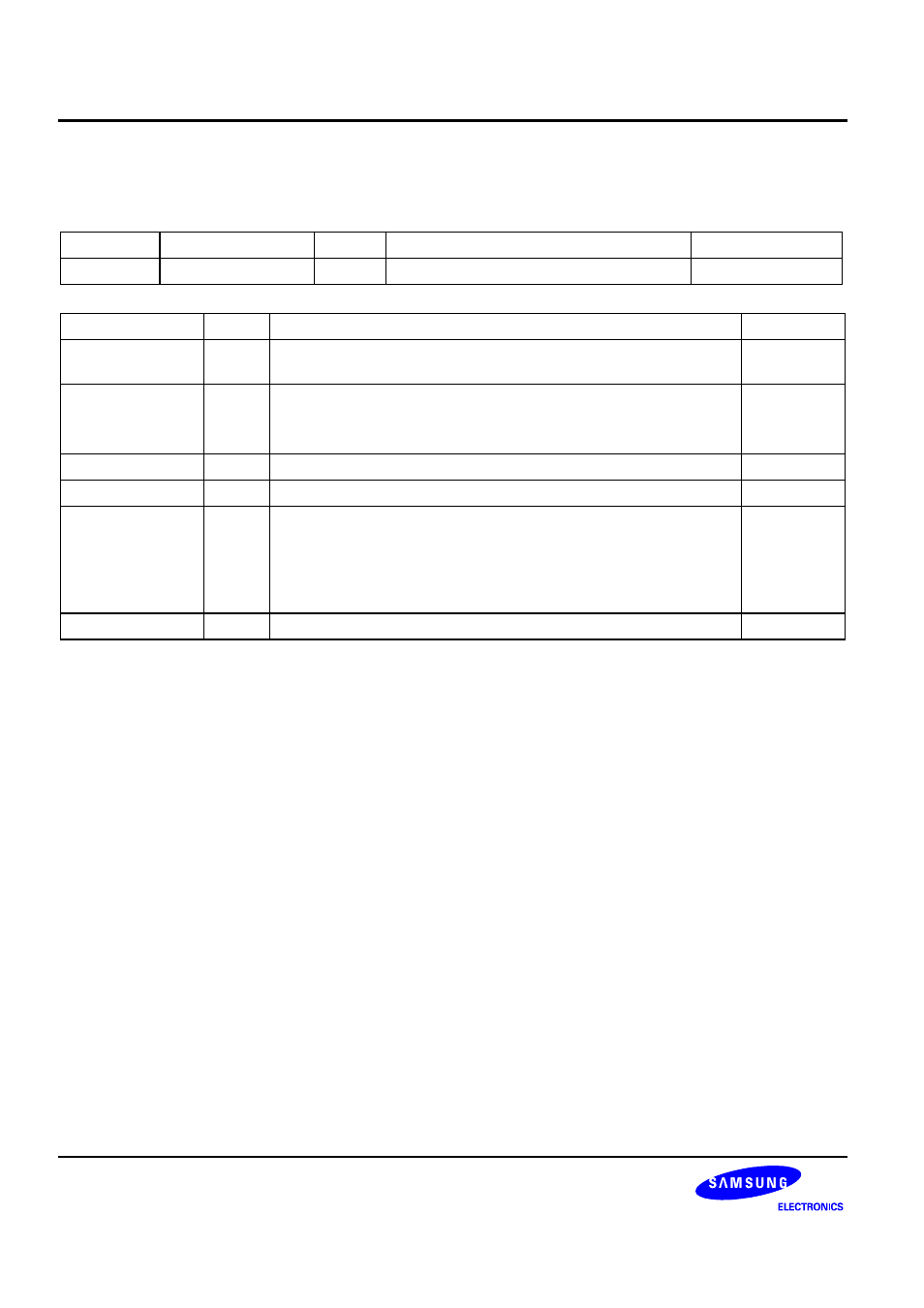

CAMERA INTERFACE SPECIAL REGISTERS

SOURCE FORMAT REGISTER

Register Address R/W

Description

Reset

Value

CISRCFMT

0x4F000000

RW

Input Source Format Register

0

CISRCFMT Bit

Description

Initial

State

ITU601_656n [31]

0 = ITU-R BT.656 YCbCr 8-bit mode enable

1 = ITU-R BT.601 YCbCr 8-bit mode enable

0

UVOffset [30]

Cb,Cr Value Offset Control.

0 = +0 (normally used) - for YCbCr

1 = +128

- for YUV

0

Reserved

[29]

This bit is reserved and the value must be 0.

0

SourceHsize

[28:16] Source Horizontal Pixel Number (must be multiple of 8)

0

Order422 [15:14]

Input YcbCr order inform for input 8-bit mode

00 = YCbYCr

01 = YCrYCb

10 = CbYCrY

11 = CrYCbY

0

SourceVsize

[12:0]

Source Vertical Pixel Number

0

Note : We recommend a following sequence for preventing FIFO overflow at first frame of capture operation in CODEC path

1. CISRCFMT[31] <- '1'

2. S/W reset

3. Initialize the Camera I/F

4. Start Capturing

1. CISRCFMT[31] <- '1'

2. S/W reset

3. Initialize the Camera I/F

4. CISRCFMT[31] <- '0' //for ITU 656 foramt

6. Start Capturing

7. Clear Overflow of codec on First ISR