Samsung S3C2440A User Manual

Page 25

PRODUCT OVERVIEW

S3C2440A RISC MICROPROCESSOR

1-24

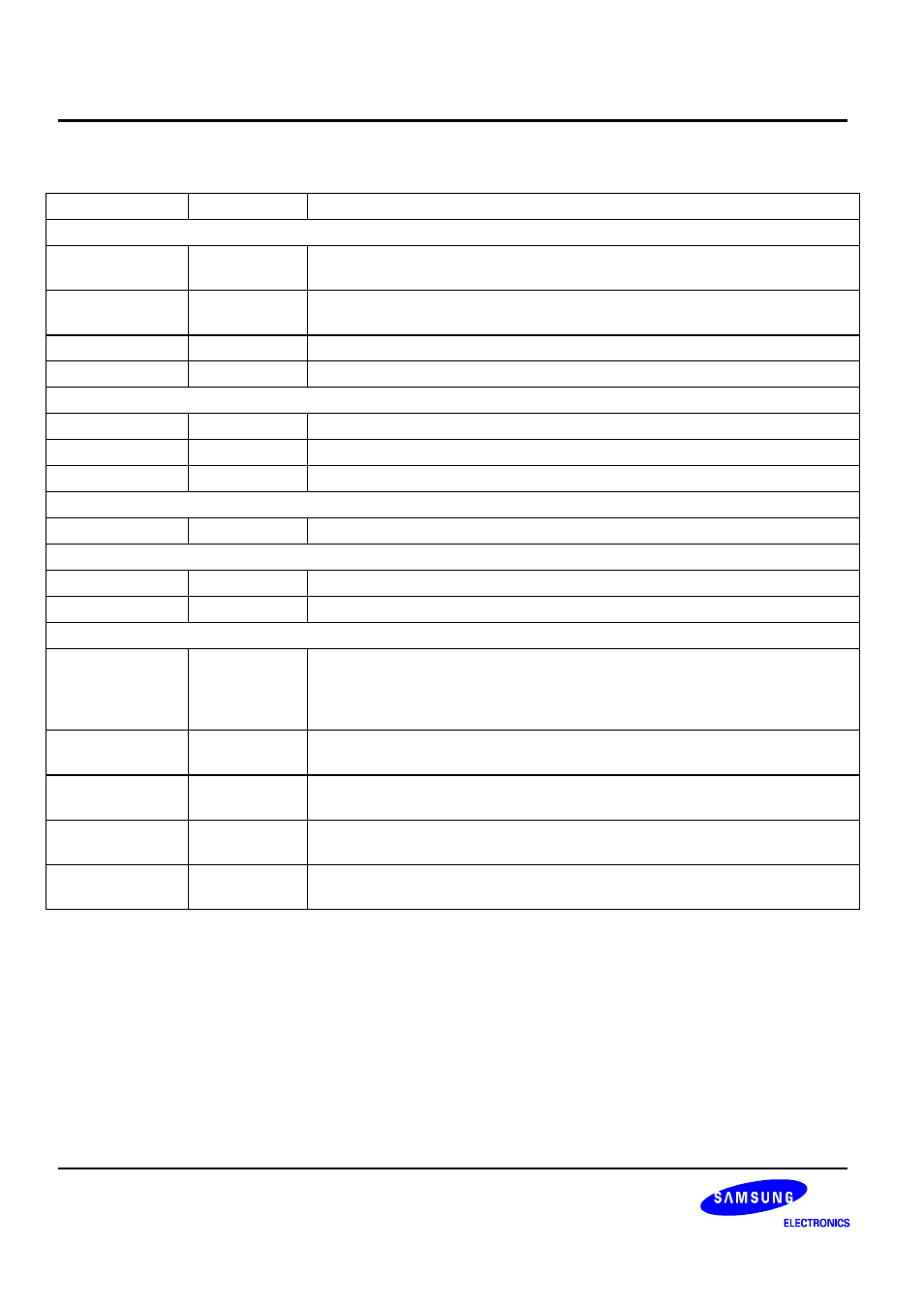

Table 1-3. S3C2440A Signal Descriptions (Sheet 4 of 6)

Signal Input/Output

Description

SPI

SPIMISO[1:0]

IO

SPIMISO is the master data input line, when SPI is configured as a master.

When SPI is configured as a slave, these pins reverse its role.

SPIMOSI[1:0]

IO

SPIMOSI is the master data output line, when SPI is configured as a master.

When SPI is configured as a slave, these pins reverse its role.

SPICLK[1:0] IO

SPI

clock

nSS[1:0]

I

SPI chip select(only for slave mode)

SD

SDDAT[3:0]

IO

SD receive/transmit data

SDCMD

IO

SD receive response/ transmit command

SDCLK O

SD

clock

General Port

GPn[129:0]

IO

General input/output ports (some ports are output only)

TIMMER/PWM

TOUT[3:0] O

Timer

output[3:0]

TCLK[1:0]

I

External timer clock input

JTAG TEST LOGIC

nTRST

I

nTRST(TAP Controller Reset) resets the TAP controller at start.

If debugger is used, A 10K pull-up resistor has to be connected.

If debugger(black ICE) is not used, nTRST pin must be issued by a low active

pulse(Typically connected to nRESET).

TMS

I

TMS (TAP Controller Mode Select) controls the sequence of the TAP

controller's states. A 10K pull-up resistor has to be connected to TMS pin.

TCK

I

TCK (TAP Controller Clock) provides the clock input for the JTAG logic.

A 10K pull-up resistor must be connected to TCK pin.

TDI

I

TDI (TAP Controller Data Input) is the serial input for test instructions and data.

A 10K pull-up resistor must be connected to TDI pin.

TDO

O

TDO (TAP Controller Data Output) is the serial output for test instructions and

data.