Samsung S3C2440A User Manual

Page 180

S3C2440A RISC MICROPROCESSOR

MEMORY CONTROLLER

DEC.13, 2002

5-15

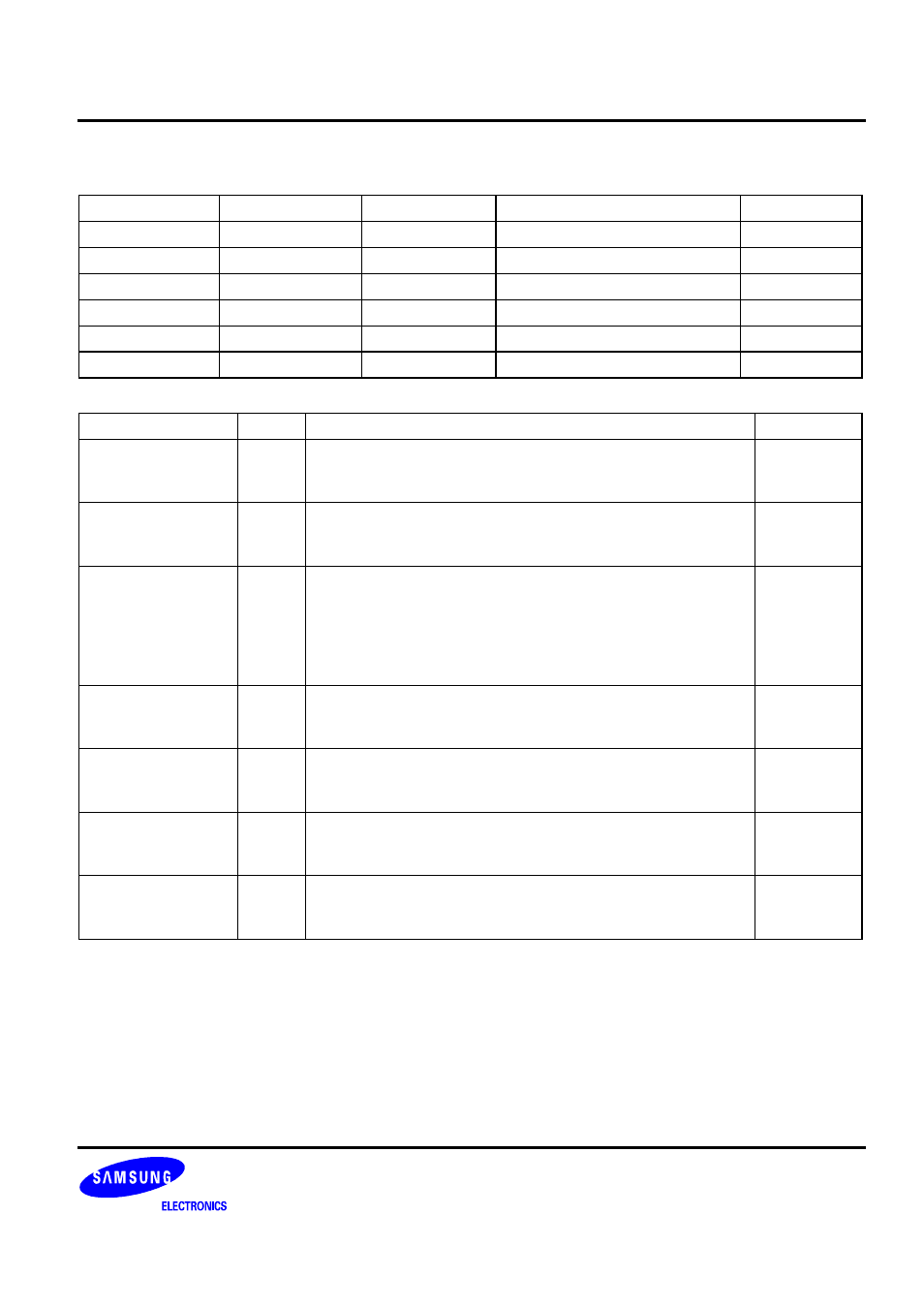

BANK CONTROL REGISTER (BANKCONn: nGCS0-nGCS5)

Register Address R/W

Description

Reset

Value

BANKCON0

0x48000004

R/W

Bank 0 control register

0x0700

BANKCON1

0x48000008

R/W

Bank 1 control register

0x0700

BANKCON2

0x4800000C

R/W

Bank 2 control register

0x0700

BANKCON3

0x48000010

R/W

Bank 3 control register

0x0700

BANKCON4

0x48000014

R/W

Bank 4 control register

0x0700

BANKCON5

0x48000018

R/W

Bank 5 control register

0x0700

BANKCONn Bit

Description

Initial

State

Tacs

[14:13] Address set-up time before nGCSn

00 = 0 clock 01 = 1 clock

10 = 2 clocks 11 = 4 clocks

00

Tcos

[12:11] Chip selection set-up time before nOE

00 = 0 clock 01 = 1 clock

10 = 2 clocks 11 = 4 clocks

00

Tacc [10:8]

Access

cycle

000 = 1 clock

001 = 2 clocks

010 = 3 clocks

011 = 4 clocks

100 = 6 clocks

101 = 8 clocks

110 = 10 clocks

111 = 14 clocks

Note: When nWAIT signal is used, Tacc

≥

4 clocks.

111

Tcoh

[7:6]

Chip selection hold time after nOE

00 = 0 clock 01 = 1 clock

10 = 2 clocks 11 = 4 clocks

000

Tcah

[5:4]

Address hold time after nGCSn

00 = 0 clock 01 = 1 clock

10 = 2 clocks 11 = 4 clocks

00

Tacp

[3:2]

Page mode access cycle @ Page mode

00 = 2 clocks 01 = 3 clocks

10 = 4 clocks 11 = 6 clocks

00

PMC

[1:0]

Page mode configuration

00 = normal (1 data) 01 = 4 data

10 = 8 data 11 = 16 data

00