Samsung S3C2440A User Manual

Page 457

S3C2440A RISC MICROPROCESSOR IIC-BUS INTERFACE

20-9

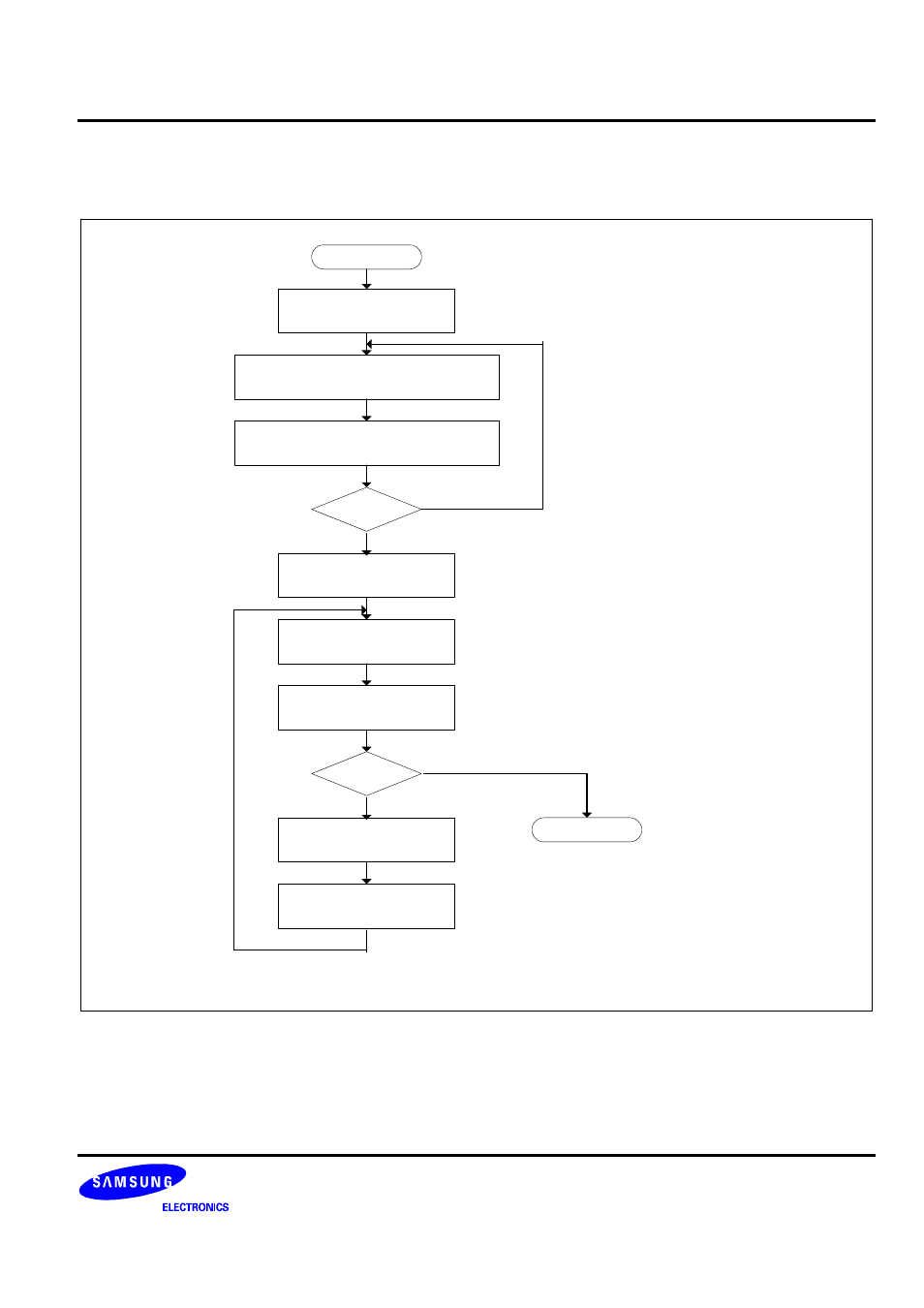

IIC detects start signal. and, IICDS

receives data.

IIC compares IICADD and IICDS (the

received slave address).

Write data to IICDS.

The IIC address match

interrupt is generated.

Clear pending bit to

resume.

The data of the IICDS is

shifted to SDA.

START

Slave Tx mode has

been configured.

END

Matched?

N

Y

Stop?

Interrupt is pending.

N

Y

Figure 20-8 Operations for Slave/Transmitter Mode

See also other documents in the category Samsung Notebooks:

- NC10 (12 pages)

- GT-P7300 (133 pages)

- M6000 (130 pages)

- M60 (201 pages)

- P55 (172 pages)

- Tablet (44 pages)

- Q45c (199 pages)

- Galaxy Tab 8.9 (188 pages)

- X22 (197 pages)

- Q46 (194 pages)

- GT-P7100 (108 pages)

- R71 (196 pages)

- Q71 (191 pages)

- M55 (161 pages)

- GT-P6210 (200 pages)

- V1.3.0 (26 pages)

- Q35 (157 pages)

- 8.9 (176 pages)

- X65 (195 pages)

- Galaxy Tab A3LSGHI987 (146 pages)

- GALAXY Tab SGH-I987 (149 pages)

- Q30 (127 pages)

- NP270E5V (27 pages)

- NP670Z5E (157 pages)

- NP275E5E (135 pages)

- NP270E5GI (134 pages)

- NP535U3C (154 pages)

- NP370R5E (133 pages)

- XE500T1C (117 pages)

- XE500T1C (122 pages)

- NP270E5UE (27 pages)

- NP930X5J-S01US (115 pages)

- NP930X5J-S01US (149 pages)

- NP900X3D-A03US (138 pages)

- NP900X4D-A03US (129 pages)

- NP470R5E-K01UB (120 pages)

- NP470R5E-K01UB (126 pages)

- NP470R5E-K01UB (125 pages)

- NP700Z3C-S01US (156 pages)

- NP355V4C-A01VE (140 pages)

- NP940X3G-S01US (149 pages)

- NP940X3G-S01US (147 pages)

- NP915S3G-K02US (118 pages)

- NP915S3G-K02US (145 pages)