Samsung S3C2440A User Manual

Page 511

S3C2440A RISC MICROPROCESSOR AC97 CONTROLLER

24-9

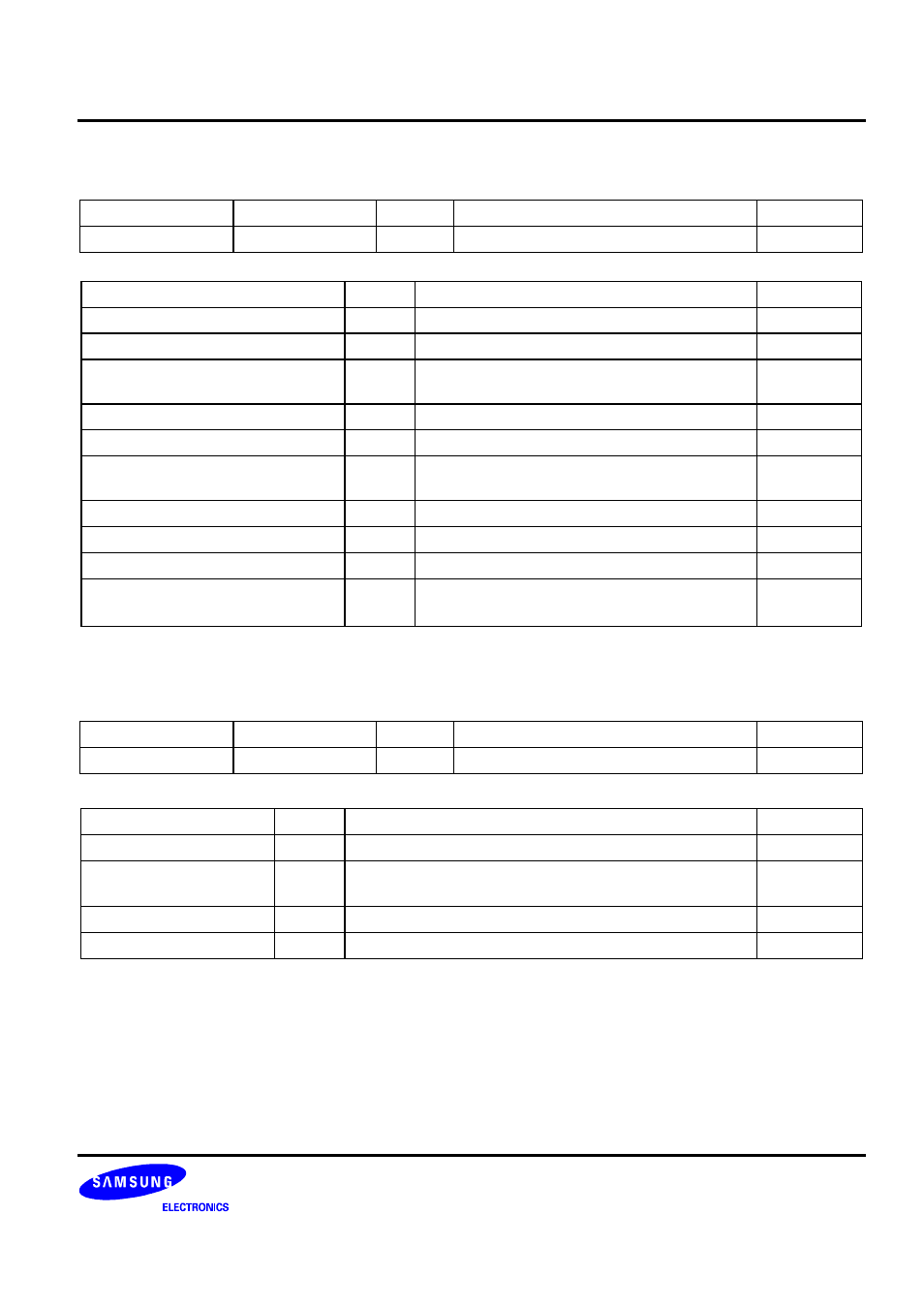

AC97 GLOBAL STATUS REGISTER (AC_GLBSTAT)

Register Address

R/W

Description

Reset

Value

AC_GLBSTAT

0x5B000004

R

AC97 Global Status Register

0x00000000

AC_GLBSTAT Bit

Description

Initial

State

Reserved [31:23]

0x00

Codec Ready Interrupt

[22]

0 : Not requested 1 : Requested

0

PCM Out Channel Underrun

Interrupt

[21]

0 : Not requested 1 : Requested

0

PCM In Channel Overrun Interrupt

[20]

0 : Not requested 1 : Requested

0

MIC In Channel Overrun Interrupt

[19]

0 : Not requested 1 : Requested

0

PCM Out Channel Threshold

Interrupt

[18]

0 : Not requested 1 : Requested

0

PCM In Channel Threshold Interrupt

[17]

0 : Not requested 1 : Requested

0

MIC In Channel Threshold Interrupt

[16]

0 : Not requested 1 : Requested

0

Reserved [15:3]

0x000

Controller Main State

[2:0]

000 : Idle 001 : Init 010 : Ready

011 : Active 100 : LP 101 : Warm

000

AC97 CODEC COMMAND REGISTER (AC_CODEC_CMD)

Register Address

R/W

Description

Reset

Value

AC_CODEC_CMD

0x5B000008

R/W

AC97 Codec Command Register

0x00000000

AC_CODEC_CMD Bit

Description

Initial

State

Reserved

[31:24]

0x00

Read enable

[23]

0 : Command write

(NOTE)

1 : Status read

0

Address

[22:16]

CODEC Command Address

0x00

Data

[15:0]

CODEC Command Data

0x0000

Note: When the commands are written on the AC_CODDEC_CMD register, it is recommended that the delay time between

the command and the next command is more than 1/48 Hz.