Samsung S3C2440A User Manual

Page 468

IIS-BUS INTERFACE

S3C2440A RISC MICROPROCESSOR

21-6

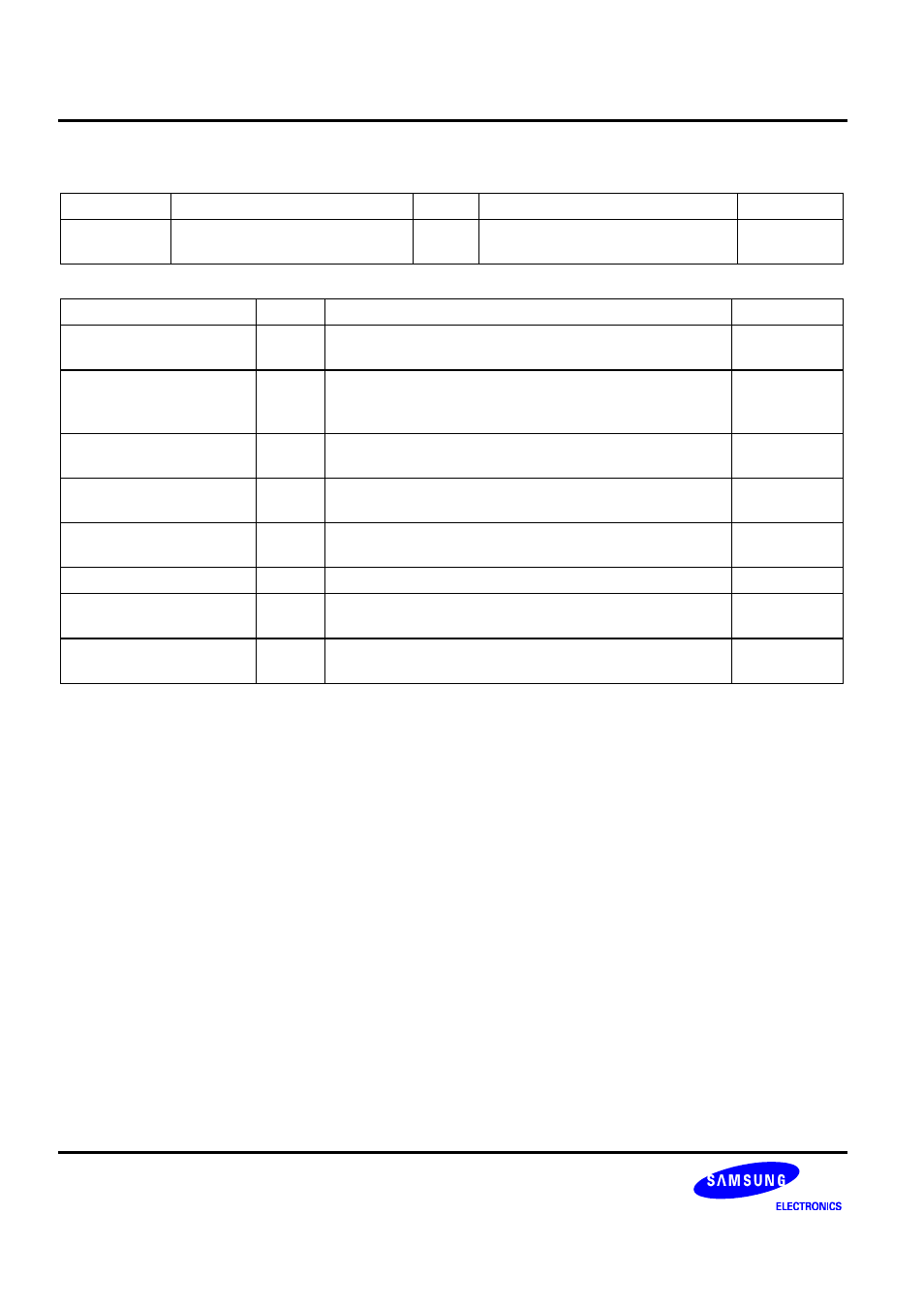

IIS MODE REGISTER (IISMOD) REGISTER

Register Address R/W

Description

Reset

Value

IISMOD

0x55000004 (Li/W, Li/HW, Bi/W)

0x55000006 (Bi/HW)

R/W

IIS mode register

0x0

IISMOD Bit

Description

Initial

State

Master Clock Select

[9]

Master clock select

0 = PCLK

1 = MPLLin

0

Master/slave mode select

[8]

0 = Master mode (IISLRCK and IISCLK are output

mode).

1 = Slave mode (IISLRCK and IISCLK are input mode).

0

Transmit/receive mode

select

[7:6]

00 = No transfer 01 = Receive mode

10 = Transmit mode 11 = Transmit and receive mode

00

Active level of left/right

channel

[5]

0 = Low for left channel (High for right channel)

1 = High for left channel (Low for right channel)

0

Serial interface format

[4]

0 = IIS compatible format

1 = MSB (Left)-justified format

0

Serial data bit per channel

[3]

0 = 8-bit 1 = 16-bit

0

Master clock frequency

select

[2]

0 = 256fs 1 = 384fs

(fs : sampling frequency)

0

Serial bit clock frequency

select

[1:0]

00 = 16fs 01 = 32fs

10 = 48fs 11 = N/A

00

Notes

1. The IISMOD register is accessible for each halfword and wordunit using STRH/STR and LDRH/LDR instructions or short

int/int type pointer in Little/Big endian mode.

2. (Li/HW/W) : Little/HalfWord/Word.

(Bi/HW/W) : Big/HalfWord/Word.