Samsung S3C2440A User Manual

Page 320

UART

S3C2440A RISC MICROPROCESSOR

11-16

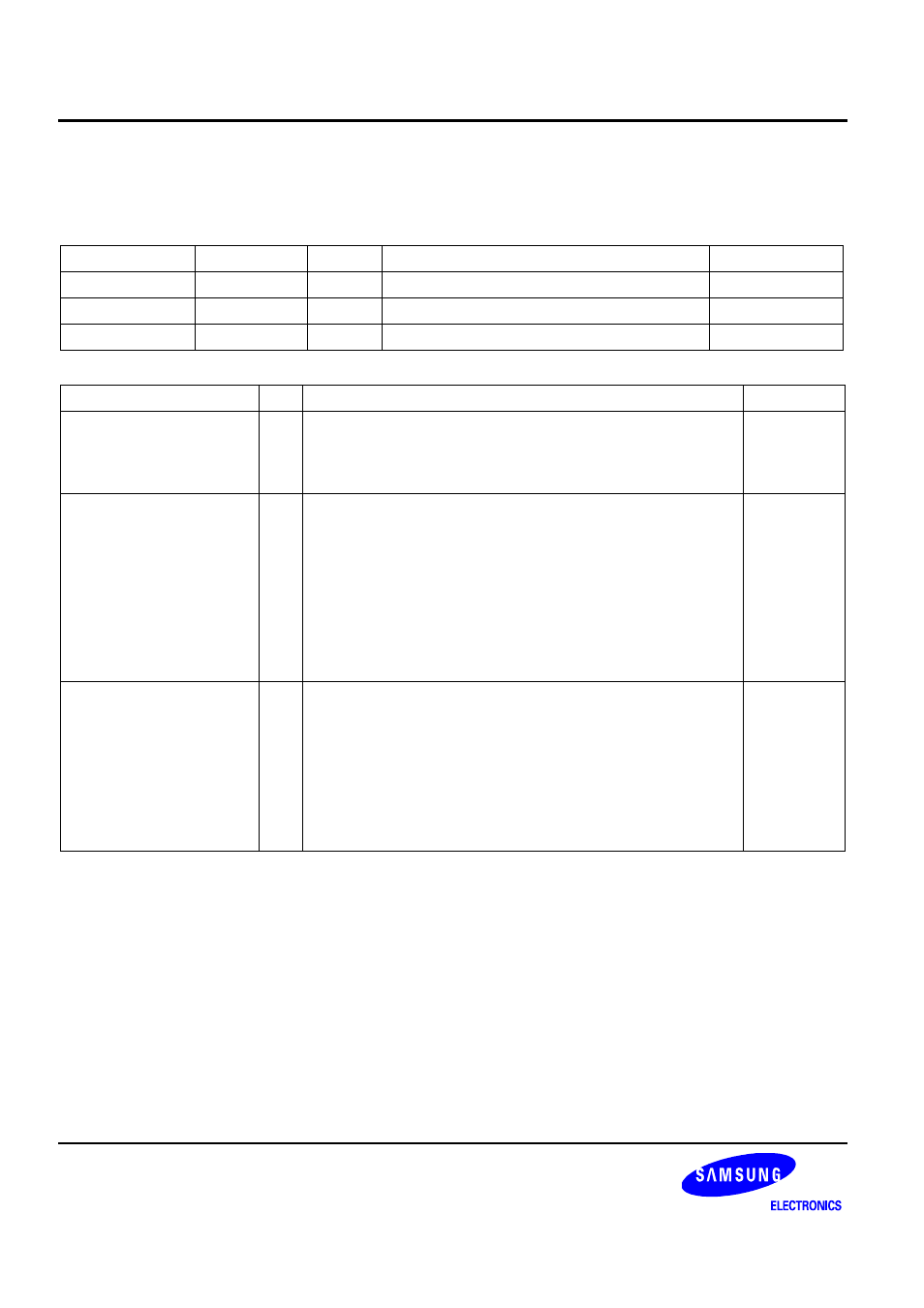

UART TX/RX STATUS REGISTER

There are three UART Tx/Rx status registers including UTRSTAT0, UTRSTAT1 and UTRSTAT2 in the UART

block.

Register Address

R/W

Description

Reset

Value

UTRSTAT0

0x50000010

R

UART channel 0 Tx/Rx status register

0x6

UTRSTAT1

0x50004010

R

UART channel 1 Tx/Rx status register

0x6

UTRSTAT2

0x50008010

R

UART channel 2 Tx/Rx status register

0x6

UTRSTATn Bit

Description

Initial

State

Transmitter empty

[2]

Set to 1 automatically when the transmit buffer register has no

valid data to transmit and the transmit shift register is empty.

0 = Not empty

1 = Transmitter (transmit buffer & shifter register) empty

1

Transmit buffer empty

[1]

Set to 1 automatically when transmit buffer register is empty.

0 =The buffer register is not empty

1 = Empty

(In Non-FIFO mode, Interrupt or DMA is requested.

In FIFO mode, Interrupt or DMA is requested, when Tx

FIFO Trigger Level is set to 00 (Empty))

If the UART uses the FIFO, users should check Tx FIFO

Count bits and Tx FIFO Full bit in the UFSTAT register instead

of this bit.

1

Receive buffer data ready

[0]

Set to 1 automatically whenever receive buffer register

contains valid data, received over the RXDn port.

0 = Empty

1 = The buffer register has a received data

(In Non-FIFO mode, Interrupt or DMA is requested)

If the UART uses the FIFO, users should check Rx FIFO

Count bits and Rx FIFO Full bit in the UFSTAT register

instead of this bit.

0