Samsung S3C2440A User Manual

Page 232

S3C2440A RISC MICROPROCESSOR

CLOCK & POWER MANAGEMENT

7

-25

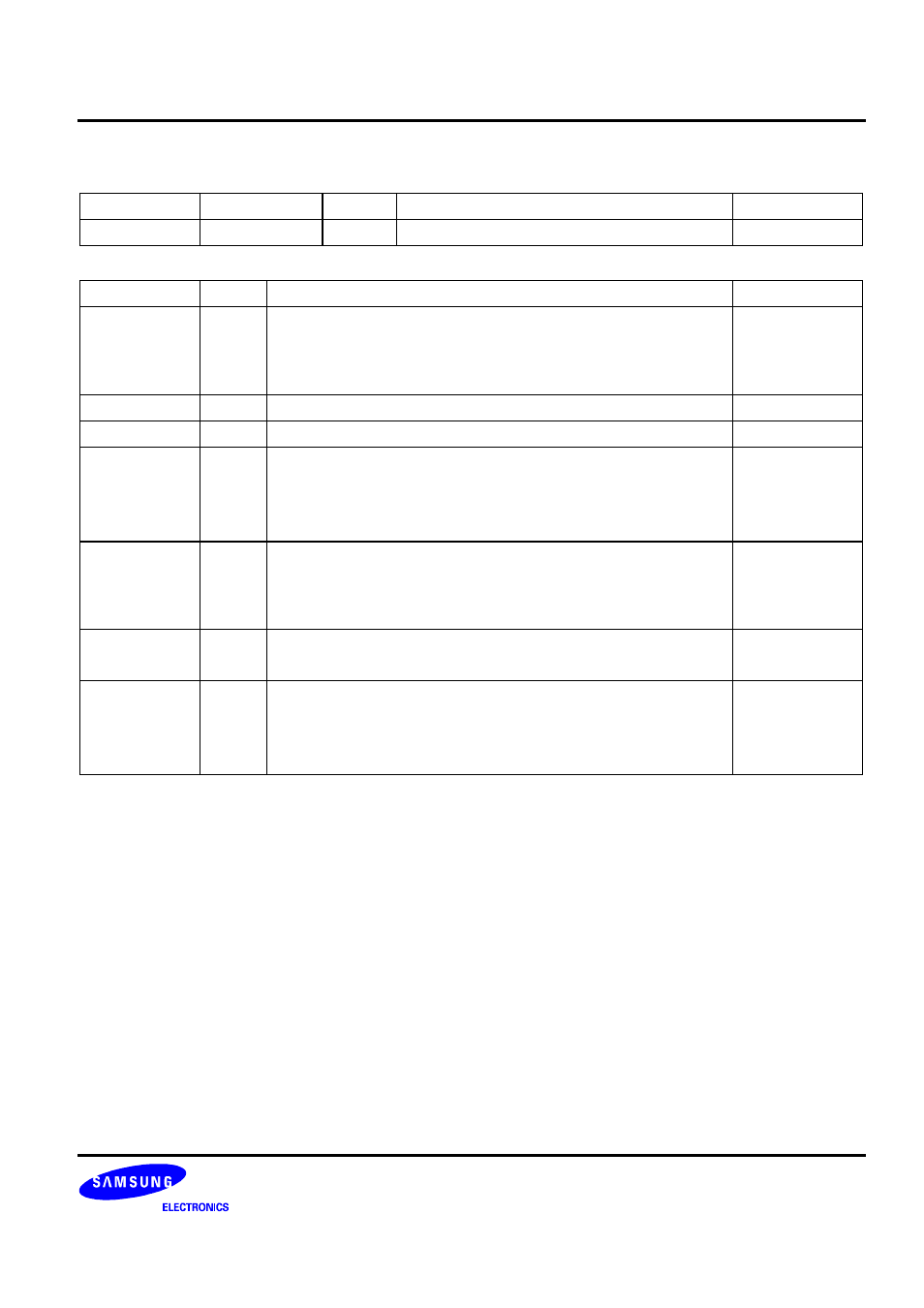

CAMERA CLOCK DIVIDER (CAMDIVN) REGISTER

Register Address R/W

Description

Reset

Value

CAMDIVN

0x4C000018

R/W

Camera clock divider register

0x00000000

CAMDIVN Bit

Description

Initial

State

DVS_EN

[12]

0:DVS OFF

ARM core will run normally with FCLK(MPLLout).

1:DVS ON

ARM core will run at the same clock as system clock(HCLK).

0

Reserved [11]

0

Reserved [10]

0

HCLK4_HALF

[9]

HDIVN division rate change bit, when CLKDIVN[2:1]=10b.

0: HCLK = FCLK/4

1: HCLK= FCLK/8

Refer the CLKDIV register.

0

HCLK3_HALF [8]

HDIVN division rate change bit, when CLKDIVN[2:1]=11b.

0: HCLK = FCLK/3

1: HCLK= FCLK/6

Refer the CLKDIV register.

0

CAMCLK_SEL

[4]

0:Use CAMCLK with UPLL output(CAMCLK=UPLL output).

1:CAMCLK is divided by CAMCLK_DIV value.

0

CAMCLK_DIV

[3:0]

CAMCLK divide factor setting register(0 – 15).

Camera clock = UPLL / [(CAMCLK_DIV +1)x2].

This bit is valid when CAMCLK_SEL=1.

0

- NC10 (12 pages)

- GT-P7300 (133 pages)

- M6000 (130 pages)

- M60 (201 pages)

- P55 (172 pages)

- Tablet (44 pages)

- Q45c (199 pages)

- Galaxy Tab 8.9 (188 pages)

- X22 (197 pages)

- Q46 (194 pages)

- GT-P7100 (108 pages)

- R71 (196 pages)

- Q71 (191 pages)

- M55 (161 pages)

- GT-P6210 (200 pages)

- V1.3.0 (26 pages)

- Q35 (157 pages)

- 8.9 (176 pages)

- X65 (195 pages)

- Galaxy Tab A3LSGHI987 (146 pages)

- GALAXY Tab SGH-I987 (149 pages)

- Q30 (127 pages)

- NP270E5V (27 pages)

- NP670Z5E (157 pages)

- NP275E5E (135 pages)

- NP270E5GI (134 pages)

- NP535U3C (154 pages)

- NP370R5E (133 pages)

- XE500T1C (117 pages)

- XE500T1C (122 pages)

- NP270E5UE (27 pages)

- NP930X5J-S01US (115 pages)

- NP930X5J-S01US (149 pages)

- NP900X3D-A03US (138 pages)

- NP900X4D-A03US (129 pages)

- NP470R5E-K01UB (120 pages)

- NP470R5E-K01UB (126 pages)

- NP470R5E-K01UB (125 pages)

- NP700Z3C-S01US (156 pages)

- NP355V4C-A01VE (140 pages)

- NP940X3G-S01US (149 pages)

- NP940X3G-S01US (147 pages)

- NP915S3G-K02US (118 pages)

- NP915S3G-K02US (145 pages)