9 timers and counters, Timer/counter list, Description – KEYENCE Visual KV Series User Manual

Page 42: Timer/counter list description

1.3 Device Configuration

3-18

1

Chapter 1 Programming

1.3.9

Timers and Counters

Timers and counters can be set in a program, and their outputs can be used as

contacts elsewhere in the program. [There is no restriction on the contact type (N.O.

or N.C.) and the order of use.]

A same number can be assigned to only one timer or counter. For example, T005

and C005 cannot be used in the same program.

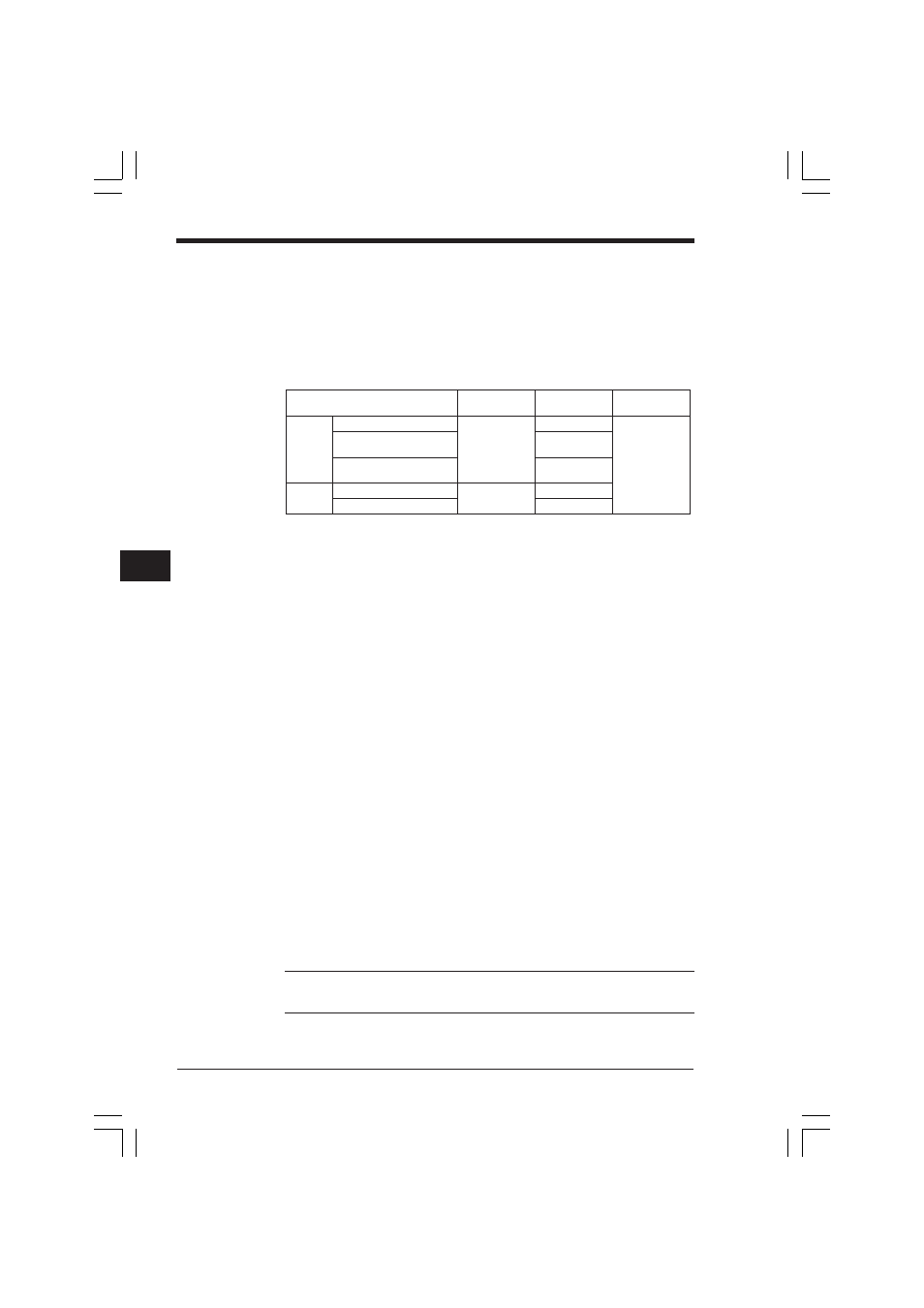

Timer/Counter list

Description

■ Timers

•

When 0.1-s timers (TMR) and high-speed 0.001-s timers (TMS) are used as

contacts, the "Tnnn" No. is used for both types. However, the form for setting is

different. "TMRnnn#ddddd" is used for 0.1-s timers, "TMHnnn#ddddd" is used for

high-speed 0.01-s timers, and "TMSnnn#ddddd" is used for high-speed 1-ms

timers (nnn = timer No, ddddd = timer set value).

•

In a single program, different timer Nos. must be assigned to each of TMRnnn,

TMHnnn, and TMSnnn.

•

When the PLC is stopped, all timers are reset and their current values become

equivalent to set values.

■ Counters

•

When counters (C) and up/down counters (UDC) are used as contacts, the

"Cnnn" No. is used for both types. However, the form for setting is different.

"Cnnn#ddddd" is used for counters, while "UDCnnn#ddddd" is used for up/down

counters.

•

In one program, different numbers must be assigned to each of the counters and

up/down counters.

•

Even when operation is stopped, each counter stores whatever value it has at

that time.

➮ "TMR instruction" (p.3-67), "TMH instruction" (p.3-68), "TMS instruction" (p.3-69), "C instruction" (p.3-

72), "UDC instruction" (p.3-76).

■ High-speed counters and high-speed counter comparators

The Visual KV Se ries is equipped with two high-speed counters (CTH0 and CTH1)

and four high-speed counter comparators (CTC0, CTC1, CTC2, and CTC3) with a

30-kHz input response speed (frequency), two phases, and size of 16 or 24 bits.

Note: When a high-speed counter or high-speed counter comparator will be used as

a 24-bit device, a set value is required to be stored in a data memory using the

MEMSW instruction.

➮ For details about high-speed counters and high-speed counter comparators, refer to "Chapter 4 High-

speed Counters" (p.3-203).

e

m

a

N

t

c

a

t

n

o

C

l

i

o

C

)

n

o

i

t

c

u

r

t

s

n

i

(

r

e

b

m

u

N

r

e

m

i

T

)

r

e

m

i

t

s

-

1

.

0

(

r

e

m

i

T

9

4

2

T

o

t

0

0

0

T

9

4

2

o

t

0

0

0

R

M

T

l

a

t

o

t

n

i

0

5

2

r

e

m

i

t

d

e

e

p

s

-

h

g

i

H

)

r

e

m

i

t

s

-

1

0

.

0

(

9

4

2

o

t

0

0

0

H

M

T

r

e

m

i

t

s

m

-

1

d

e

e

p

s

-

h

g

i

H

)

r

e

m

i

t

s

-

1

0

0

.

0

(

9

4

2

o

t

0

0

0

S

M

T

r

e

t

n

u

o

C

r

e

t

n

u

o

C

9

4

2

C

o

t

0

0

0

C

9

4

2

o

t

0

0

0

C

r

e

t

n

u

o

c

n

w

o

d

/

p

U

9

4

2

o

t

0

0

0

C

D

U

KVNKA Chap 01P.p65

08.3.11, 11:49 AM

18