2 outline of high-speed counters, Visual kv series – KEYENCE Visual KV Series User Manual

Page 230

4.2 Outline of High-speed Counters

3-206

Visual KV

Series

4

Chapter 4 High-speed Counters

4.2

Outline of High-speed Counters

This section describes the outline and specifications for high-speed counters and

high-speed counter comparators featured with the Visual KV Series.

4.2.1

High-speed Counters and High-speed Counter Compara-

tors

The high-speed counter is a hardware-based counter that can count high-speed

pulses that cannot be counted by counters written in main routines (C or UDC).

(Pulses with a maximum frequency of 30 kHz can be counted.). *

High-speed counter comparators are hardware-based comparators that compare

their preset value with the current value of one of the a high-speed counters.

Both counters and comparators perform processing with hardware rather than

software programs, enabling high-speed performance independent of the scan time.

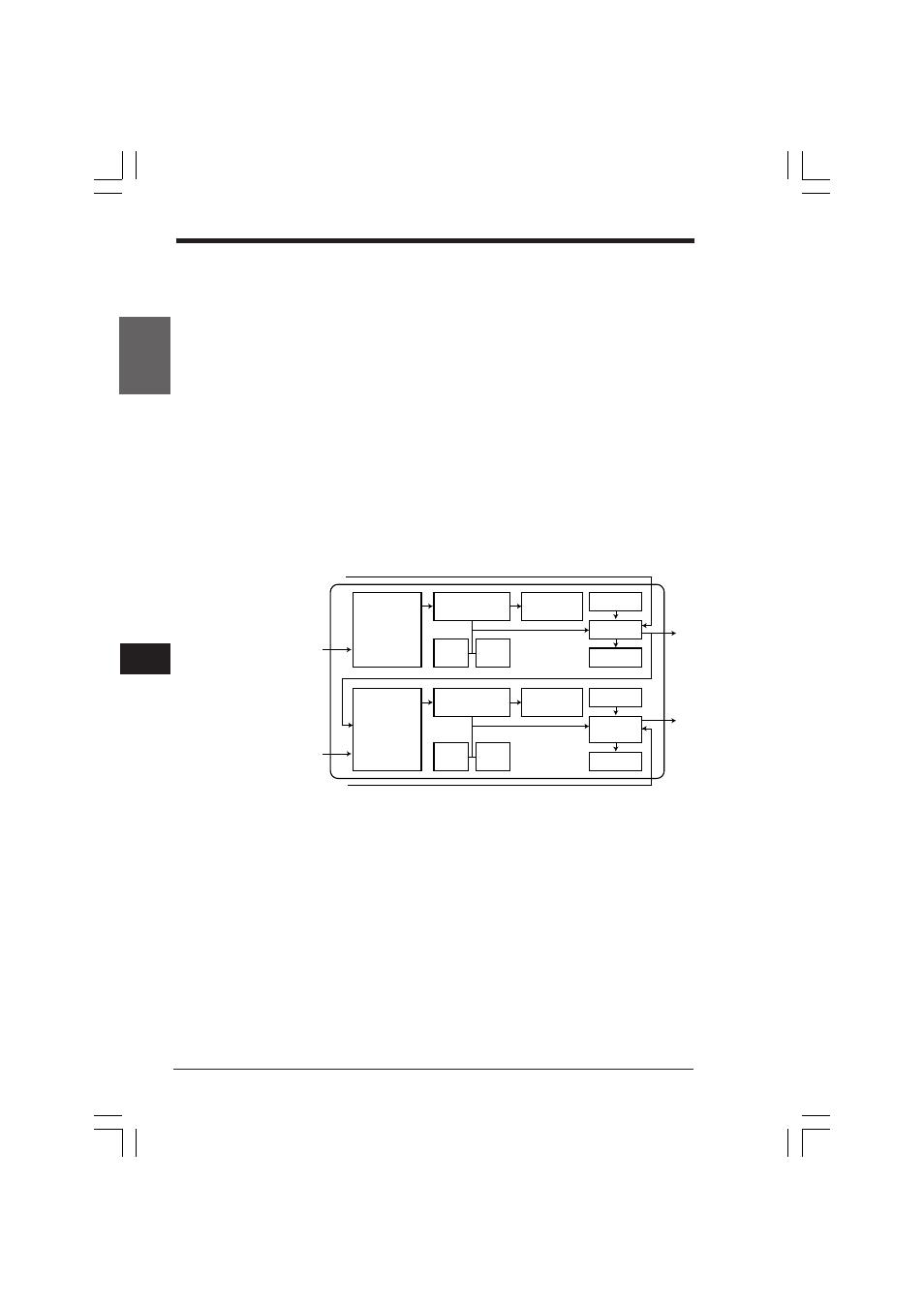

Structure of high-speed counters and high-speed counter comparators

The Visual KV PLC has two high-speed counters, each equipped with two high-

speed counter comparators and dedicated internal clocks.

Block diagram of high-speed counters

1. With the KV-10xx, the external input relay for CTH0 is 0004 (phase A)/0000

(phase B), and for CTH1 is 0005 (phase A)/0001 (phase B).

2. With the KV-10xx, the preset input relay for CTH0 is 0002, and for CTH1 is 0003.

For KV-10/80 user's

Max. response frequency: 10 kHz

*

2100 0.8 µs

2101 6.4 µs

2102 102.4 µs

2200 0.4 µs

2201 0.8 µs

2202 3.2 µs

CTC2

CTH1

CTC3

DM1932, DM1933(INT2)

DM1934, DM1935(INT3)

2203 to 2214

INT CTC2

INT CTC3

2200 (1.0 µs)

2201 (10.0 µs)

2202 (100.0µs)

0500

0005/0007

CTC0

CTH0

CTC1

DM1928, DM1929(INT0)

DM1930, DM1931(INT1)

2103 to 2114

INT CTC0

INT CTC1

2100 (1.0 µs)

2101 (10.0 µs)

2102 (100.0 µs)

0004/0006

0005

(0007)

0004

(0006)

0008 (RESET) 2.

0009 (RESET) 2.

0500

0501

Phase A

Phase B

Internal clocks*

External input

16-bit high-speed

counter

high-speed

counter

comparator

high-speed

counter

comparator

Input capture device

Special utility relay

Control circuit

Input capture device

Internal clocks*

External input

16-bit high-speed

counter

high-speed

counter

comparator

high-speed

counter

comparator

Special utility relay

Control circuit

Phase A

Phase B

Internal connection

for external clock

KVNKA Chap 04_1.p65

08.3.11, 0:06 PM

206