Eicra - external interrupt control register a – Rainbow Electronics ATmega3290P_V User Manual

Page 55

55

ATmega329/3290/649/6490

2552H–AVR–11/06

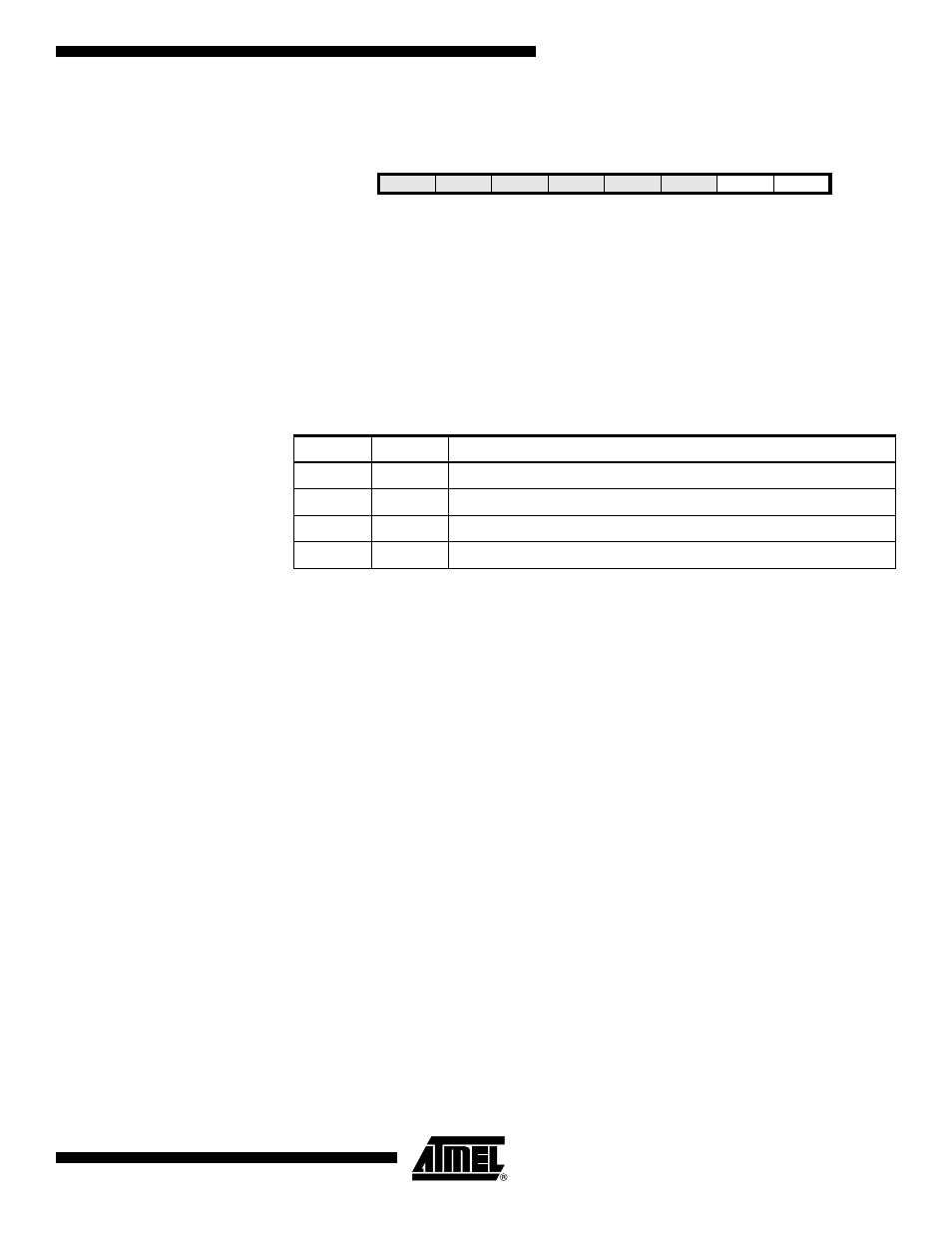

EICRA – External Interrupt

Control Register A

The External Interrupt Control Register A contains control bits for interrupt sense

control.

• Bit 1, 0 – ISC01, ISC00: Interrupt Sense Control 0 Bit 1 and Bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the

corresponding interrupt mask are set. The level and edges on the external INT0 pin that

activate the interrupt are defined in Table 24. The value on the INT0 pin is sampled

before detecting edges. If edge or toggle interrupt is selected, pulses that last longer

than one clock period will generate an interrupt. Shorter pulses are not guaranteed to

generate an interrupt. If low level interrupt is selected, the low level must be held until

the completion of the currently executing instruction to generate an interrupt.

Bit

7

6

5

4

3

2

1

0

–

–

–

–

–

–

ISC01

ISC00

EICRA

Read/Write

R

R

R

R

R

R

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

Table 24. Interrupt 0 Sense Control

ISC01

ISC00

Description

0

0

The low level of INT0 generates an interrupt request.

0

1

Any logical change on INT0 generates an interrupt request.

1

0

The falling edge of INT0 generates an interrupt request.

1

1

The rising edge of INT0 generates an interrupt request.