Overview, Block diagram, Figure 3. block diagram – Rainbow Electronics ATmega3290P_V User Manual

Page 4

4

ATmega329/3290/649/6490

2552H–AVR–11/06

Overview

The ATmega329/3290/649/6490 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architec-

ture. By executing powerful instructions in a single clock cycle, the ATmega329/3290/649/6490 achieves throughputs

approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

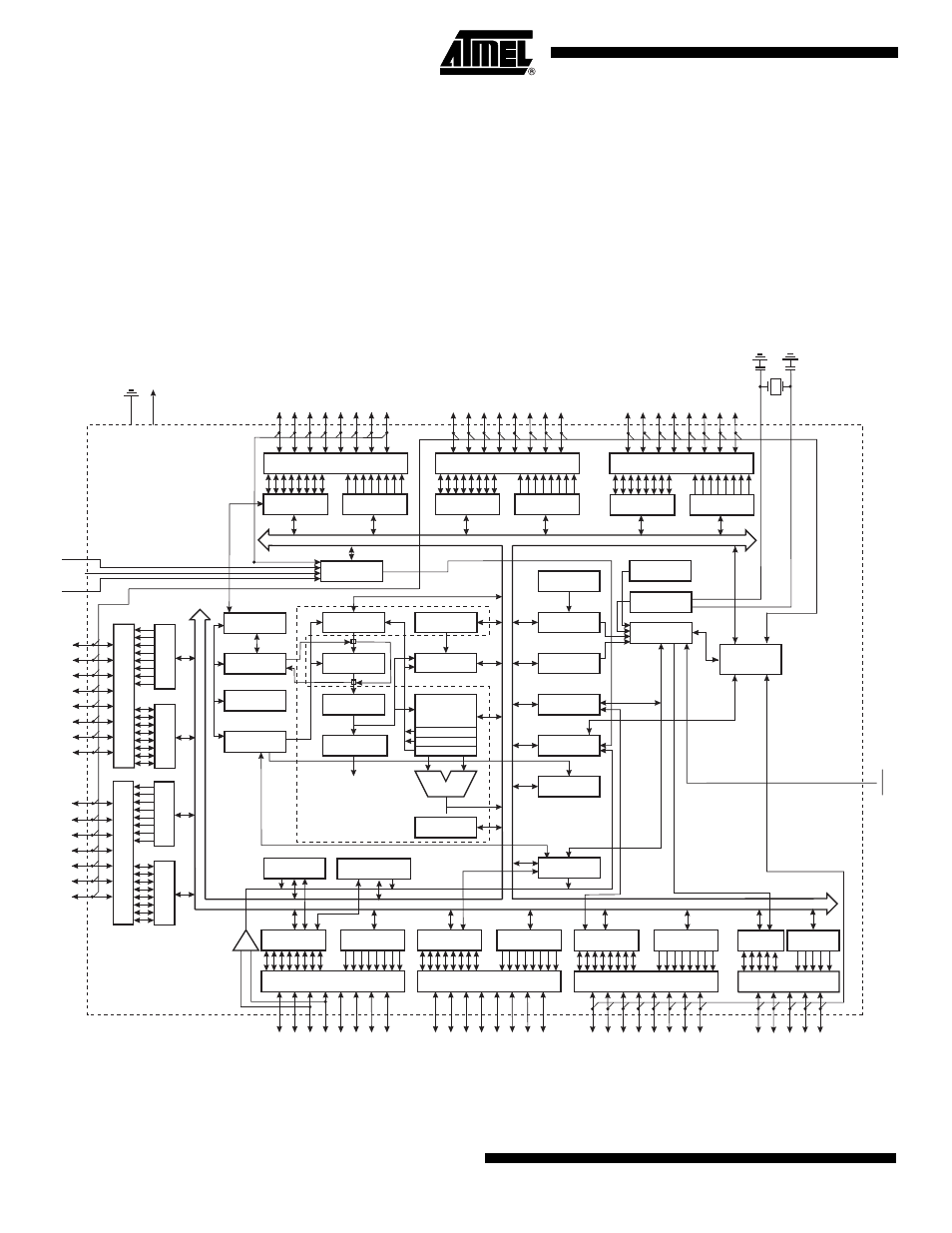

Block Diagram

Figure 3. Block Diagram

PROGRAM

COUNTER

INTERNAL

OSCILLATOR

WATCHDOG

TIMER

STACK

POINTER

PROGRAM

FLASH

MCU CONTROL

REGISTER

SRAM

GENERAL

PURPOSE

REGISTERS

INSTRUCTION

REGISTER

TIMER/

COUNTERS

INSTRUCTION

DECODER

DATA DIR.

REG. PORTB

DATA DIR.

REG. PORTE

DATA DIR.

REG. PORTA

DATA DIR.

REG. PORTD

DATA REGISTER

PORTB

DATA REGISTER

PORTE

DATA REGISTER

PORTA

DATA REGISTER

PORTD

TIMING AND

CONTROL

OSCILLATOR

INTERRUPT

UNIT

EEPROM

SPI

USART

STATUS

REGISTER

Z

Y

X

ALU

PORTB DRIVERS

PORTE DRIVERS

PORTA DRIVERS

PORTF DRIVERS

PORTD DRIVERS

PORTC DRIVERS

PB0 - PB7

PE0 - PE7

PA0 - PA7

PF0 - PF7

VCC

GND

XT

AL1

XT

AL2

CONTROL

LINES

+

-

ANALOG

COMP

ARA

T

O

R

PC0 - PC7

8-BIT DATA BUS

RESET

CALIB. OSC

DATA DIR.

REG. PORTC

DATA REGISTER

PORTC

ON-CHIP DEBUG

JTAG TAP

PROGRAMMING

LOGIC

BOUNDARY-

SCAN

DATA DIR.

REG. PORTF

DATA REGISTER

PORTF

ADC

PD0 - PD7

DATA DIR.

REG. PORTG

DATA REG.

PORTG

PORTG DRIVERS

PG0 - PG4

AGND

AREF

AVCC

UNIVERSAL

SERIAL INTERFACE

AVR CPU

LCD

CONTROLLER/

DRIVER

POR

TH DRIVERS

PH0 - PH7

D

A

T

A

DIR.

REG.

POR

T

H

D

A

T

A

REGISTER

POR

T

H

POR

TJ DRIVERS

PJ0 - PJ6

D

A

T

A

DIR.

REG.

POR

T

J

D

A

T

A

REGISTER

POR

T

J