Rainbow Electronics ATmega3290P_V User Manual

Page 253

253

ATmega329/3290/649/6490

2552H–AVR–11/06

Note:

1. Incorrect setting of the switches in Figure 116 will make signal contention and may damage the part. There are several input

choices to the S&H circuitry on the negative input of the output comparator in Figure 116. Make sure only one path is

selected from either one ADC pin, Bandgap reference source, or Ground.

If the ADC is not to be used during scan, the recommended input values from Table 111

should be used. The user is recommended not to use the differential amplifier during

scan. Switch-Cap based differential amplifier require fast operation and accurate timing

which is difficult to obtain when used in a scan chain. Details concerning operations of

the differential amplifier is therefore not provided.

The AVR ADC is based on the analog circuitry shown in Figure 116 with a successive

approximation algorithm implemented in the digital logic. When used in Boundary-scan,

the problem is usually to ensure that an applied analog voltage is measured within some

limits. This can easily be done without running a successive approximation algorithm:

apply the lower limit on the digital DAC[9:0] lines, make sure the output from the com-

parator is low, then apply the upper limit on the digital DAC[9:0] lines, and verify the

output from the comparator to be high.

The ADC need not be used for pure connectivity testing, since all analog inputs are

shared with a digital port pin as well.

When using the ADC, remember the following

•

The port pin for the ADC channel in use must be configured to be an input with pull-

up disabled to avoid signal contention.

•

In Normal mode, a dummy conversion (consisting of 10 comparisons) is performed

when enabling the ADC. The user is advised to wait at least 200ns after enabling the

ADC before controlling/observing any ADC signal, or perform a dummy conversion

before using the first result.

•

The DAC values must be stable at the midpoint value 0x200 when having the HOLD

signal low (Sample mode).

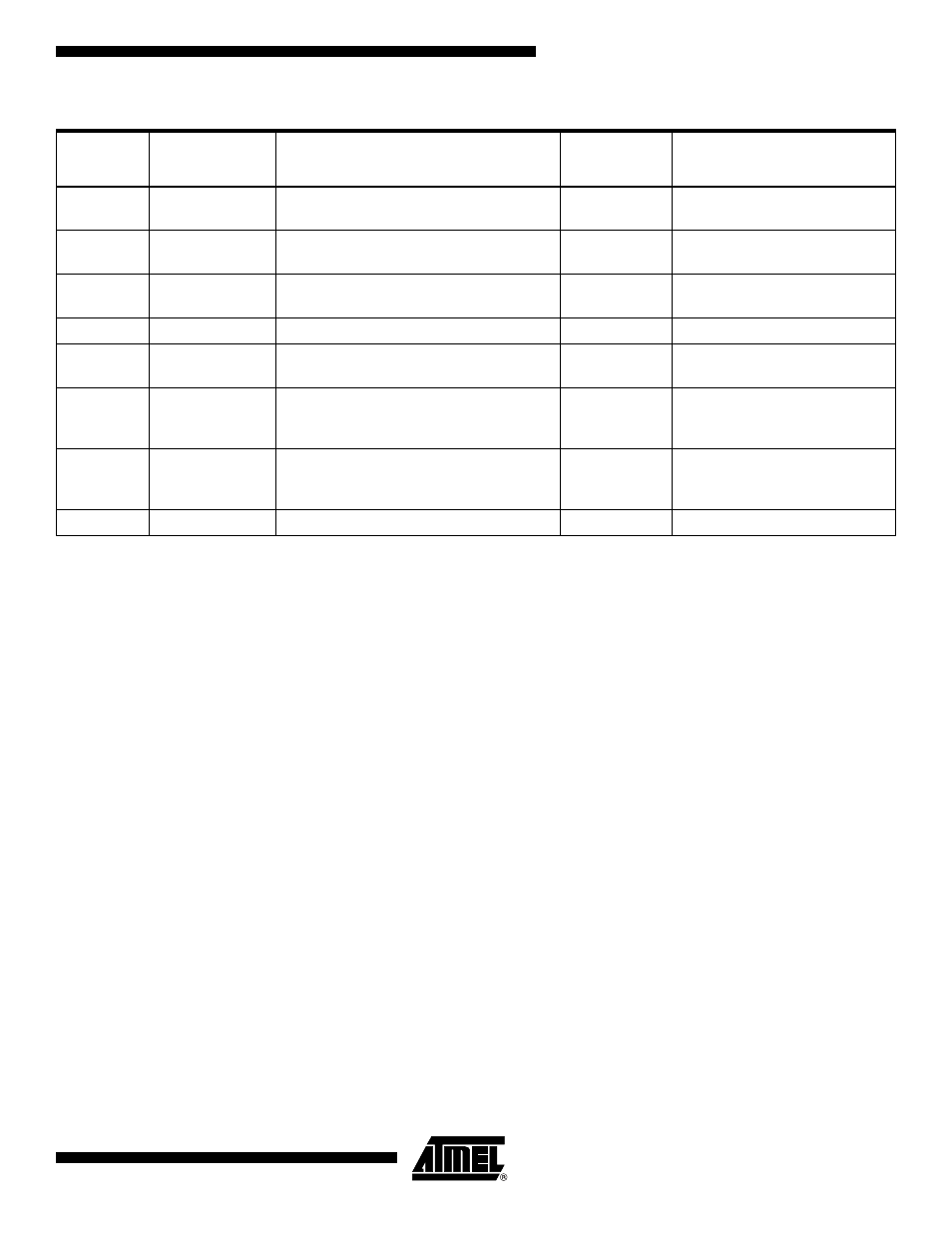

NEGSEL_2

Input

Input Mux for negative input for differential

signal, bit 2

0

0

NEGSEL_1

Input

Input Mux for negative input for differential

signal, bit 1

0

0

NEGSEL_0

Input

Input Mux for negative input for differential

signal, bit 0

0

0

PASSEN

Input

Enable pass-gate of differential amplifier.

1

1

PRECH

Input

Precharge output latch of comparator.

(Active low)

1

1

SCTEST

Input

Switch-cap TEST enable. Output from

differential amplifier send out to Port Pin

having ADC_4

0

0

ST

Input

Output of differential amplifier will settle

faster if this signal is high first two ACLK

periods after AMPEN goes high.

0

0

VCCREN

Input

Selects Vcc as the ACC reference voltage.

0

0

Table 111. Boundary-scan Signals for the ADC

(1)

(Continued)

Signal Name

Direction as seen

from the ADC

Description

Recommended

Input when not

in use

Output Values when

recommended inputs are used,

and CPU is not using the ADC