Adcl and adch - the adc data register, Adlar = 0, Adlar = 1 – Rainbow Electronics ATmega3290P_V User Manual

Page 218: Adcsrb - adc control and status register b

218

ATmega329/3290/649/6490

2552H–AVR–11/06

ADCL and ADCH – The ADC

Data Register

ADLAR = 0

ADLAR = 1

When an ADC conversion is complete, the result is found in these two registers. When

ADCL is read, the ADC Data Register is not updated until ADCH is read. Consequently,

if the result is left adjusted and no more than 8-bit precision is required, it is sufficient to

read ADCH. Otherwise, ADCL must be read first, then ADCH.

The ADLAR bit in ADMUX, and the MUXn bits in ADMUX affect the way the result is

read from the registers. If ADLAR is set, the result is left adjusted. If ADLAR is cleared

(default), the result is right adjusted.

• ADC9:0: ADC Conversion Result

These bits represent the result from the conversion, as detailed in “ADC Conversion

Result” on page 213.

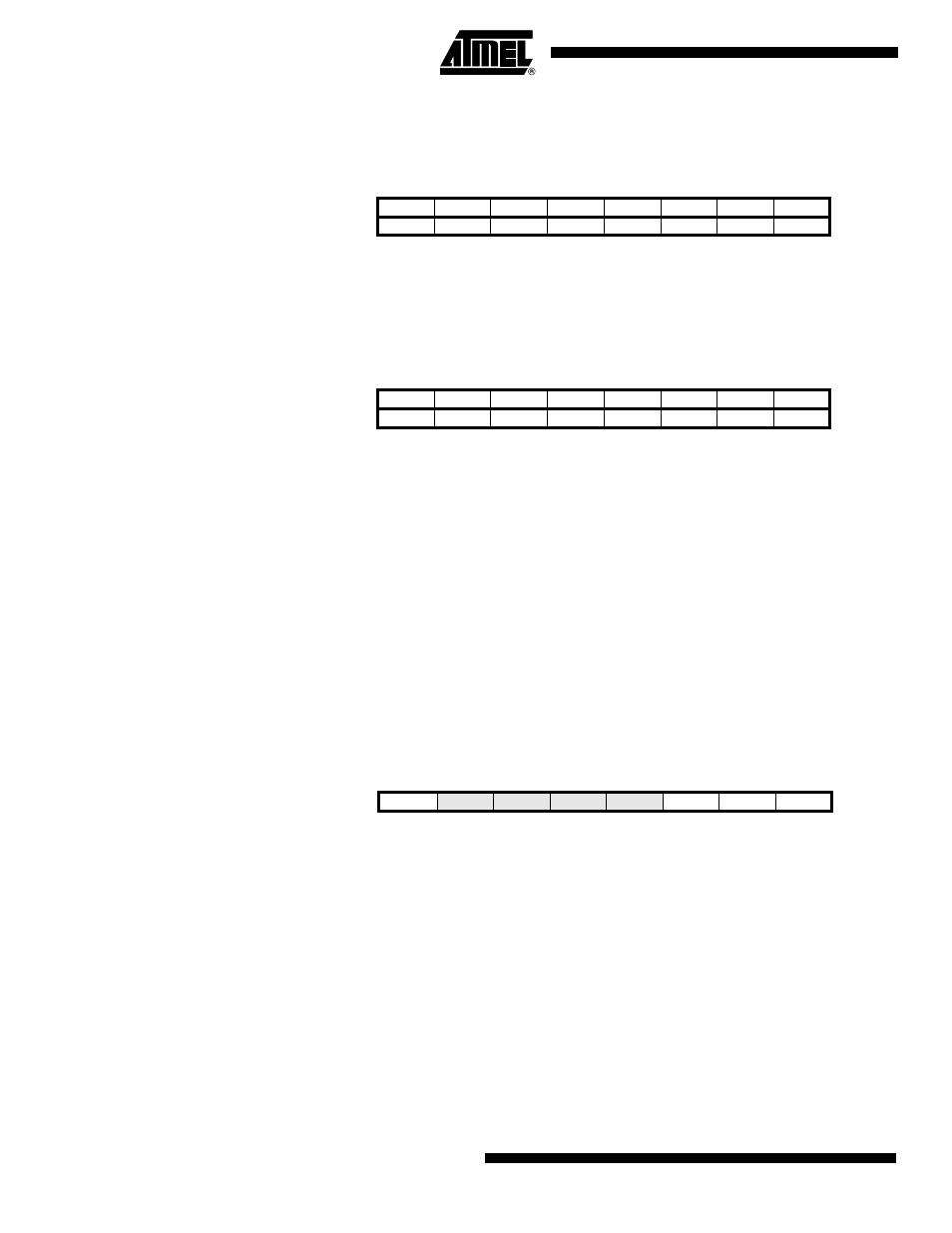

ADCSRB – ADC Control and

Status Register B

• Bit 7 – Res: Reserved Bit

This bit is reserved for future use. To ensure compatibility with future devices, this bit

must be written to zero when ADCSRB is written.

• Bit 2:0 – ADTS2:0: ADC Auto Trigger Source

If ADATE in ADCSRA is written to one, the value of these bits selects which source will

trigger an ADC conversion. If ADATE is cleared, the ADTS2:0 settings will have no

effect. A conversion will be triggered by the rising edge of the selected Interrupt Flag.

Note that switching from a trigger source that is cleared to a trigger source that is set,

will generate a positive edge on the trigger signal. If ADEN in ADCSRA is set, this will

start a conversion. Switching to Free Running mode (ADTS[2:0]=0) will not cause a trig-

ger event, even if the ADC Interrupt Flag is set

.

Bit

15

14

13

12

11

10

9

8

–

–

–

–

–

–

ADC9

ADC8

ADCH

ADC7

ADC6

ADC5

ADC4

ADC3

ADC2

ADC1

ADC0

ADCL

7

6

5

4

3

2

1

0

Read/Write

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Initial Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

ADC9

ADC8

ADC7

ADC6

ADC5

ADC4

ADC3

ADC2

ADCH

ADC1

ADC0

–

–

–

–

–

–

ADCL

7

6

5

4

3

2

1

0

Read/Write

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Initial Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

–

ACME

–

–

–

ADTS2

ADTS1

ADTS0

ADCSRB

Read/Write

R

R/W

R

R

R

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0