Data reception - the usart receiver, Receiving frames with 5 to 8 data bits, Receiving frames with 9 data bits – Rainbow Electronics ATmega3290P_V User Manual

Page 171: Data reception – the usart receiver

171

ATmega329/3290/649/6490

2552H–AVR–11/06

Data Reception – The

USART Receiver

The USART Receiver is enabled by writing the Receive Enable (RXENn) bit in the UCS-

RnB Register to one. When the Receiver is enabled, the normal pin operation of the

RxD pin is overridden by the USART and given the function as the Receiver’s serial

input. The baud rate, mode of operation and frame format must be set up once before

any serial reception can be done. If synchronous operation is used, the clock on the

XCK pin will be used as transfer clock.

Receiving Frames with 5 to 8

Data Bits

The Receiver starts data reception when it detects a valid start bit. Each bit that follows

the start bit will be sampled at the baud rate or XCK clock, and shifted into the Receive

Shift Register until the first stop bit of a frame is received. A second stop bit will be

ignored by the Receiver. When the first stop bit is received, i.e., a complete serial frame

is present in the Receive Shift Register, the contents of the Shift Register will be moved

into the receive buffer. The receive buffer can then be read by reading the UDRn I/O

location.

The following code example shows a simple USART receive function based on polling

of the Receive Complete (RXCn) Flag. When using frames with less than eight bits the

most significant bits of the data read from the UDRn will be masked to zero. The USART

has to be initialized before the function can be used.

Note:

1. See “About Code Examples” on page 8.

The function simply waits for data to be present in the receive buffer by checking the

RXCn Flag, before reading the buffer and returning the value.

Receiving Frames with 9 Data

Bits

If 9-bit characters are used (UCSZ=7) the ninth bit must be read from the RXB8n bit in

UCSRnB before reading the low bits from the UDRn. This rule applies to the FEn,

DORn and UPEn Status Flags as well. Read status from UCSRnA, then data from

UDRn. Reading the UDRn I/O location will change the state of the receive buffer FIFO

and consequently the TXB8n, FEn, DORn and UPEn bits, which all are stored in the

FIFO, will change.

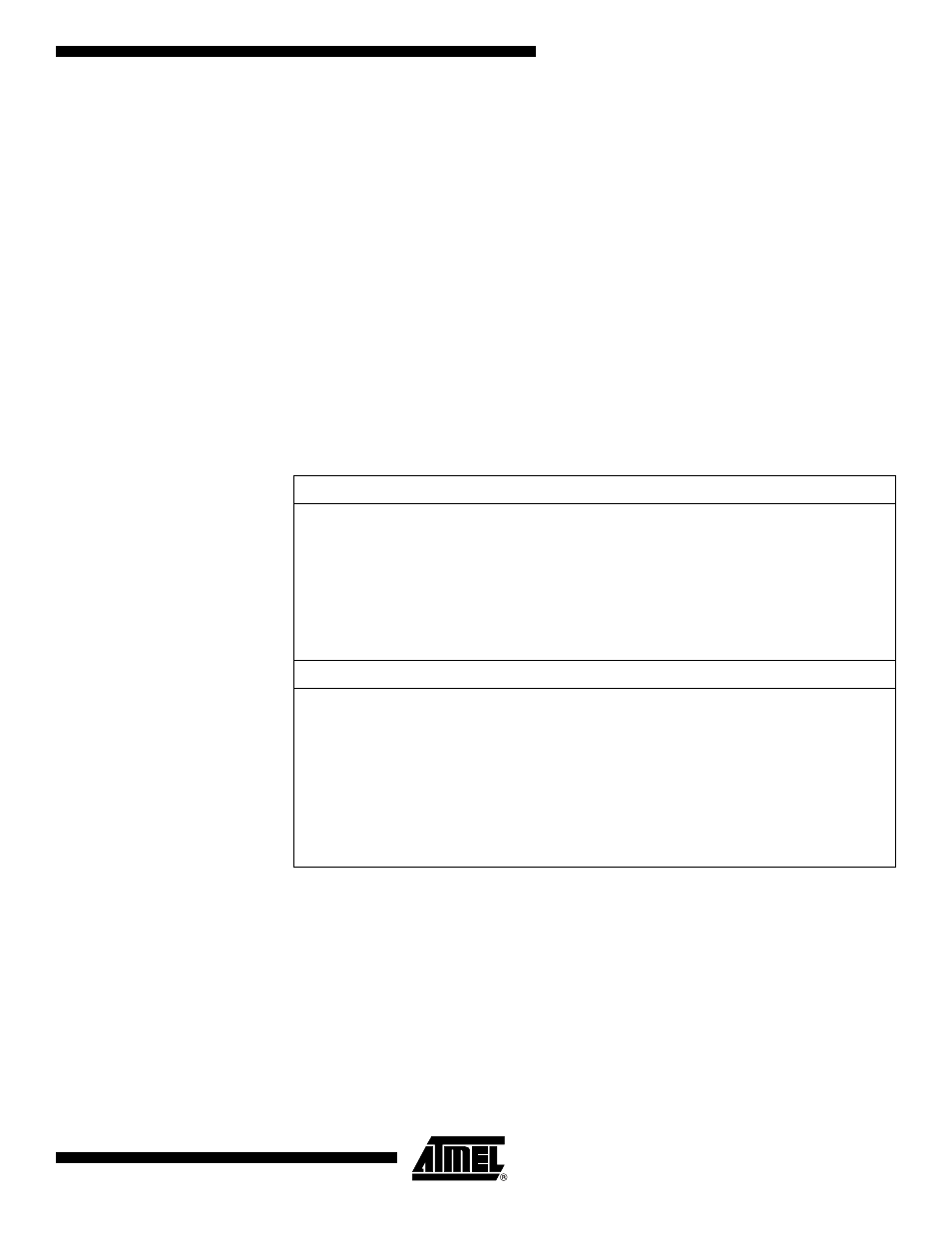

Assembly Code Example

(1)

USART_Receive:

; Wait for data to be received

sbis

UCSR0A, RXC0

rjmp

USART_Receive

; Get and return received data from buffer

in

r16, UDR0

ret

C Code Example

(1)

unsigned char

USART_Receive( void )

{

/* Wait for data to be received */

while

( !(UCSR0A & (1< ; /* Get and return received data from buffer */ return UDR0; }