Usicr - usi control register – Rainbow Electronics ATmega3290P_V User Manual

Page 197

197

ATmega329/3290/649/6490

2552H–AVR–11/06

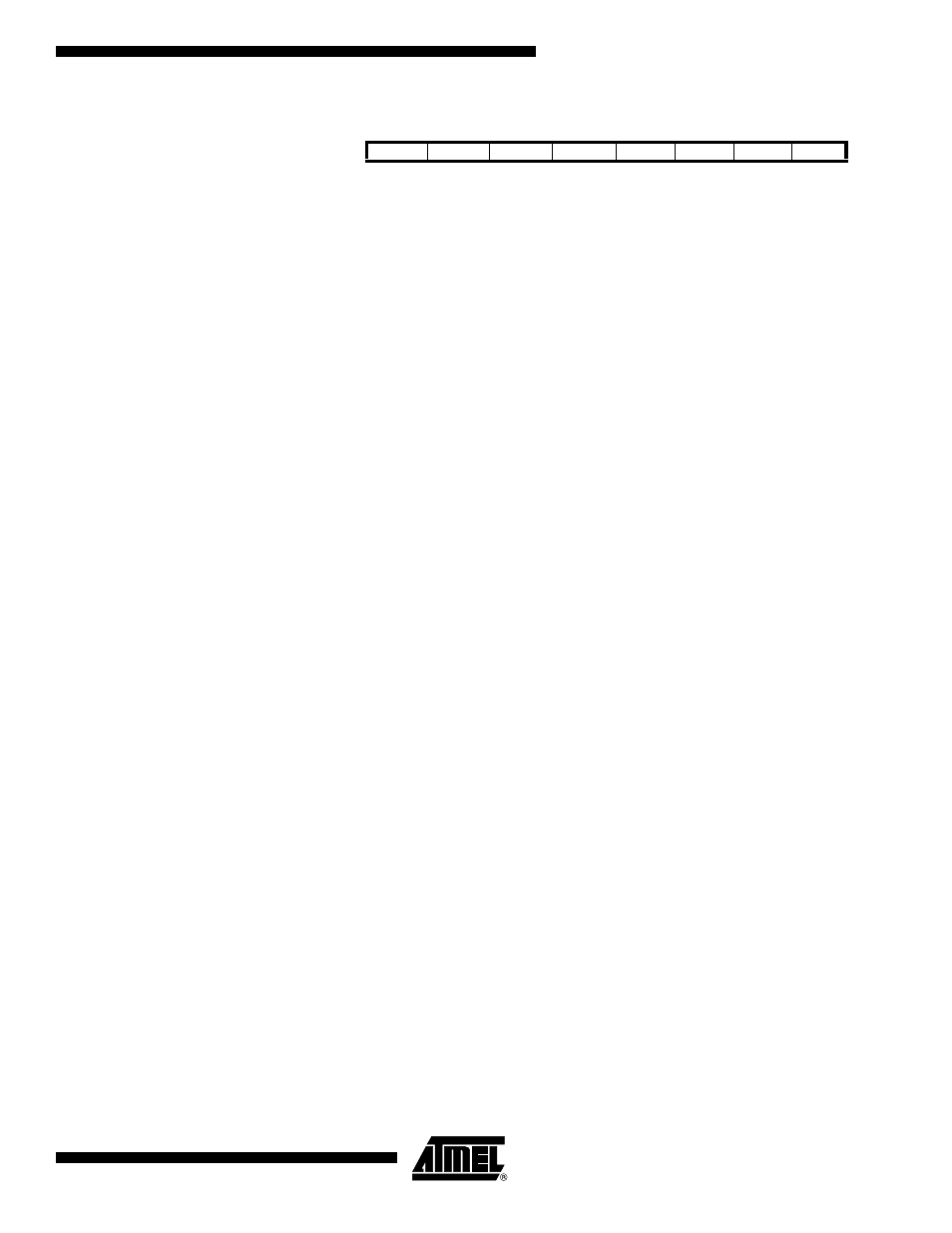

USICR – USI Control Register

The Control Register includes interrupt enable control, wire mode setting, Clock Select

setting, and clock strobe.

• Bit 7 – USISIE: Start Condition Interrupt Enable

Setting this bit to one enables the Start Condition detector interrupt. If there is a pending

interrupt when the USISIE and the Global Interrupt Enable Flag is set to one, this will

immediately be executed. Refer to the USISIF bit description on page 195 for further

details.

• Bit 6 – USIOIE: Counter Overflow Interrupt Enable

Setting this bit to one enables the Counter Overflow interrupt. If there is a pending inter-

rupt when the USIOIE and the Global Interrupt Enable Flag is set to one, this will

immediately be executed. Refer to the USIOIF bit description on page 195 for further

details.

• Bit 5..4 – USIWM1..0: Wire Mode

These bits set the type of wire mode to be used. Basically only the function of the out-

puts are affected by these bits. Data and clock inputs are not affected by the mode

selected and will always have the same function. The counter and Shift Register can

therefore be clocked externally, and data input sampled, even when outputs are dis-

abled. The relations between USIWM1..0 and the USI operation is summarized in Table

89.

Bit

7

6

5

4

3

2

1

0

USISIE

USIOIE

USIWM1

USIWM0

USICS1

USICS0

USICLK

USITC

USICR

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

W

W

Initial Value

0

0

0

0

0

0

0

0