Wdtcr - watchdog timer control register – Rainbow Electronics ATmega3290P_V User Manual

Page 46

46

ATmega329/3290/649/6490

2552H–AVR–11/06

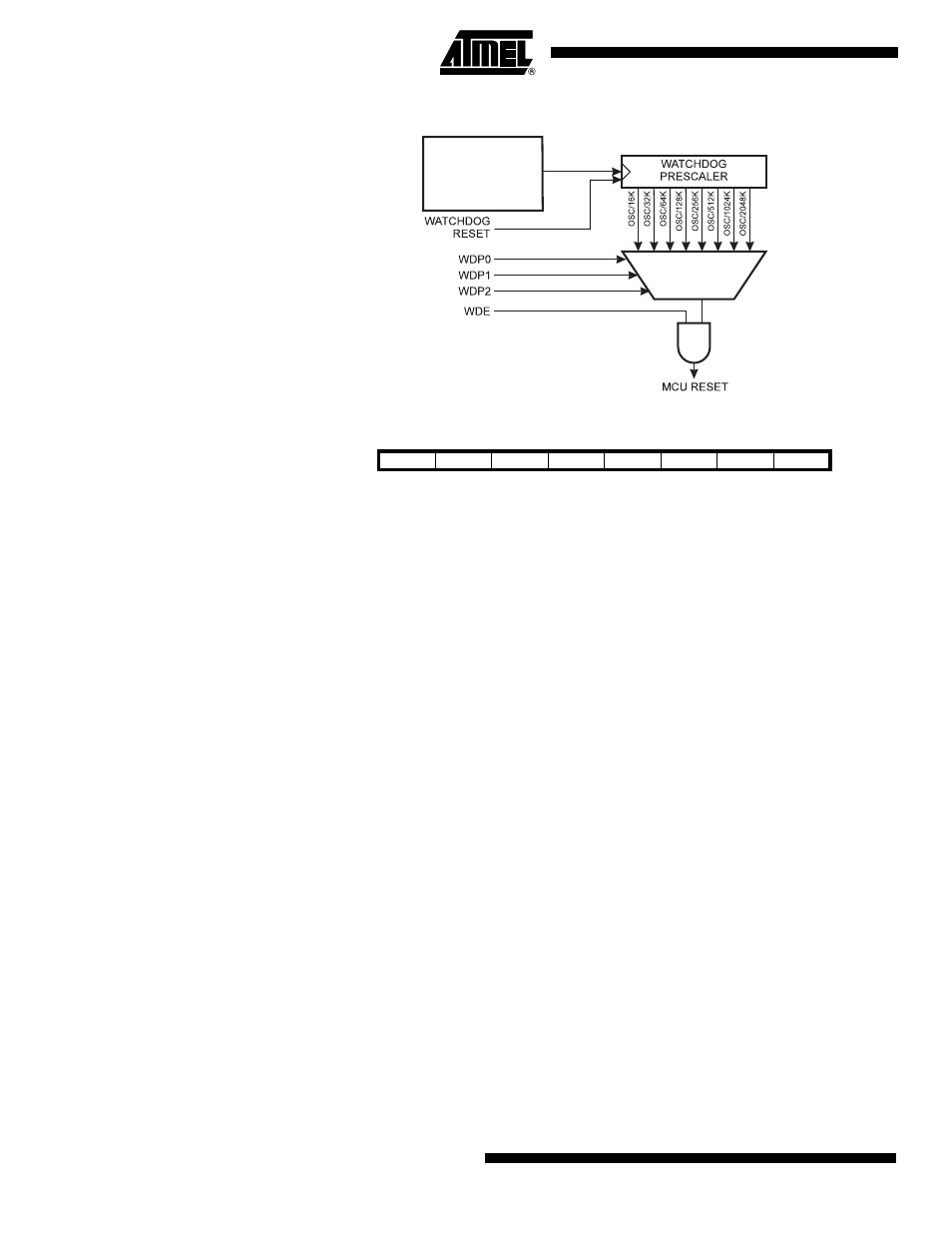

Figure 21. Watchdog Timer

WDTCR – Watchdog Timer

Control Register

• Bits 7:5 – Res: Reserved Bits

These bits are reserved bits in the ATmega329/3290/649/6490 and will always read as

zero.

• Bit 4 – WDCE: Watchdog Change Enable

This bit must be set when the WDE bit is written to logic zero. Otherwise, the Watchdog

will not be disabled. Once written to one, hardware will clear this bit after four clock

cycles. Refer to the description of the WDE bit for a Watchdog disable procedure. This

bit must also be set when changing the prescaler bits. See “Timed Sequences for

Changing the Configuration of the Watchdog Timer” on page 48.

• Bit 3 – WDE: Watchdog Enable

When the WDE is written to logic one, the Watchdog Timer is enabled, and if the WDE is

written to logic zero, the Watchdog Timer function is disabled. WDE can only be cleared

if the WDCE bit has logic level one. To disable an enabled Watchdog Timer, the follow-

ing procedure must be followed:

1.

In the same operation, write a logic one to WDCE and WDE. A logic one must be

written to WDE even though it is set to one before the disable operation starts.

2.

Within the next four clock cycles, write a logic 0 to WDE. This disables the

Watchdog.

In safety level 2, it is not possible to disable the Watchdog Timer, even with the algo-

rithm described above. See “Timed Sequences for Changing the Configuration of the

Watchdog Timer” on page 48.

• Bits 2:0 – WDP2, WDP1, WDP0: Watchdog Timer Prescaler 2, 1, and 0

The WDP2, WDP1, and WDP0 bits determine the Watchdog Timer prescaling when the

Watchdog Timer is enabled. The different prescaling values and their corresponding

Time-out Periods are shown in Table 21 on page 47.

WATCHDOG

OSCILLATOR

Bit

7

6

5

4

3

2

1

0

–

–

–

WDCE

WDE

WDP2

WDP1

WDP0

WDTCR

Read/Write

R

R

R

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0