Rainbow Electronics ATmega3290P_V User Manual

Page 158

158

ATmega329/339/649/659

2552H–AVR–11/06

be cleared, and SPIF in SPSR will become set. The user will then have to set MSTR to

re-enable SPI Master mode.

• Bit 3 – CPOL: Clock Polarity

When this bit is written to one, SCK is high when idle. When CPOL is written to zero,

SCK is low when idle. Refer to Figure 68 and Figure 69 for an example. The CPOL func-

tionality is summarized below:

• Bit 2 – CPHA: Clock Phase

The settings of the Clock Phase bit (CPHA) determine if data is sampled on the leading

(first) or trailing (last) edge of SCK. Refer to Figure 68 and Figure 69 for an example.

The CPOL functionality is summarized below:

• Bits 1, 0 – SPR1, SPR0: SPI Clock Rate Select 1 and 0

These two bits control the SCK rate of the device configured as a Master. SPR1 and

SPR0 have no effect on the Slave. The relationship between SCK and the Oscillator

Clock frequency f

osc

is shown in the following table:

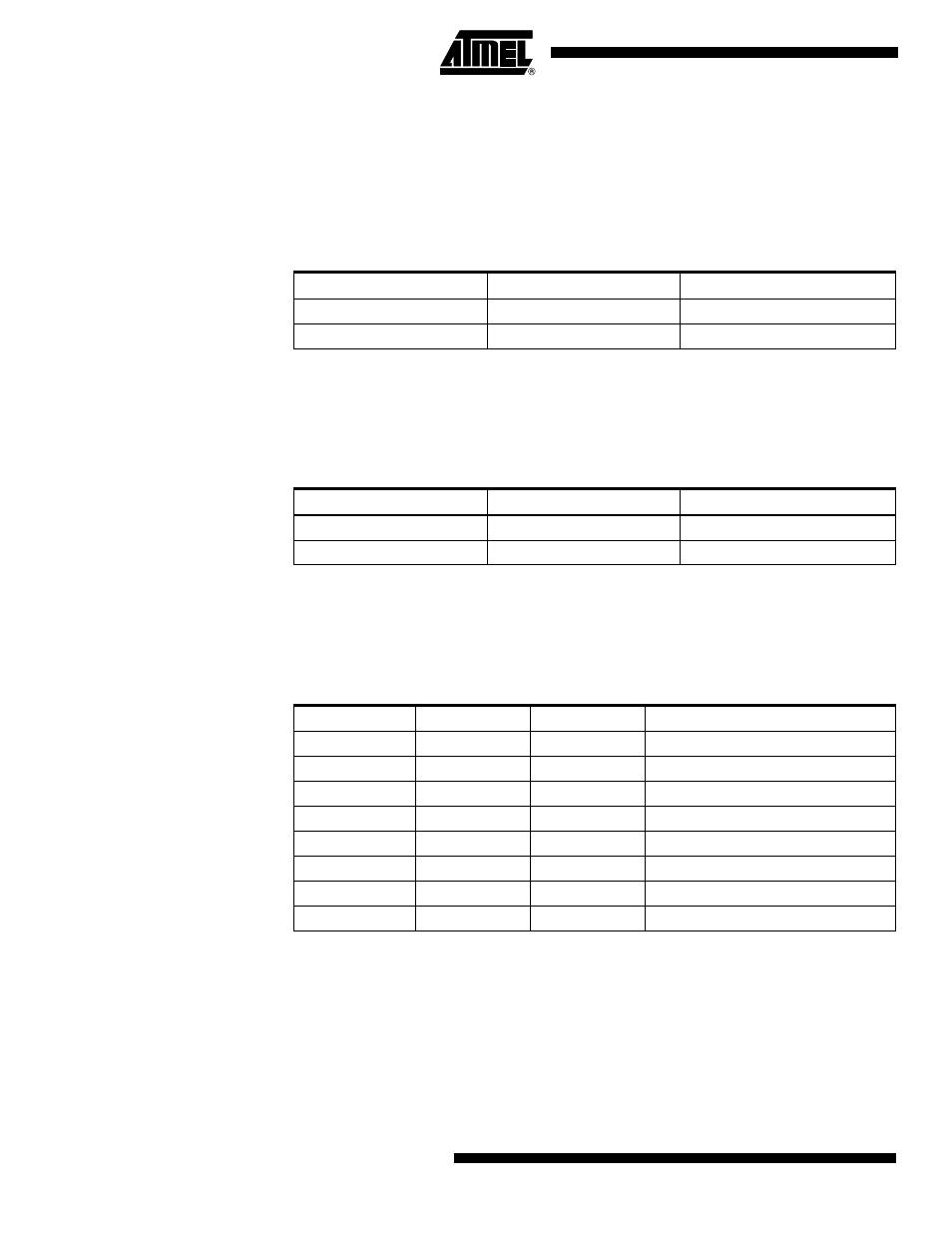

Table 73. CPOL Functionality

CPOL

Leading Edge

Trailing Edge

0

Rising

Falling

1

Falling

Rising

Table 74. CPHA Functionality

CPHA

Leading Edge

Trailing Edge

0

Sample

Setup

1

Setup

Sample

Table 75. Relationship Between SCK and the Oscillator Frequency

SPI2X

SPR1

SPR0

SCK Frequency

0

0

0

f

osc

/

4

0

0

1

f

osc

/

16

0

1

0

f

osc

/

64

0

1

1

f

osc

/

128

1

0

0

f

osc

/

2

1

0

1

f

osc

/

8

1

1

0

f

osc

/

32

1

1

1

f

osc

/

64