Rainbow Electronics W90N740 User Manual

Page 96

W90N740

- 92 -

Users should set the MDC clock setting to meet the PHY requirement (maximum 2.5MHz). Besides,

the MCLK (HCLK) frequency ranges from 10 MHz to 150 MHz (set MDC 2.5MHz).

MDCON [19]: MDC Clock On Always

Default value: 0

If this bit was set, the MDC clock will always active. Otherwise, the MDC clock will active only when

the EnMDC of MCMDR and BUSY of MIIDA are both set. In other words, the MDC clock will be turned

off after the station management command finished. This bit is only for debug.

PreSP [18]: Preamble Suppress

Default value: 0

If this bit is set, then the preamble is not sent to PHY.

BUSY [17]: Busy bit

Default value: 0

Set this bit to start a MII management read or write-operation. The MAC controller clears this bit

automatically when the operation is completed.

WR [16]: Write/Read

Default value: 0

Set this bit for a MII management write-operation. Reset the bit for a read operation.

PHYAD [12:8]: PHY Address

Default value: 0

The 5-bit address is the PHY device address to be accessed.

PHYRAD [4:0]: PHY Register Address

Default value: 0

The 5-bit address is the register address contained in the PHY to be accessed.

The MIIDA register is used to specify the control function and the data message passing for the

external physical layer device (PHY). The detail protocol and timings for the read and the write

operation, respectively, of the MII management function are illustrated as the figure below. Each bit in

the management data frame (MDIO) are synchronized at the rising edge of the MII management clock

(MDC).

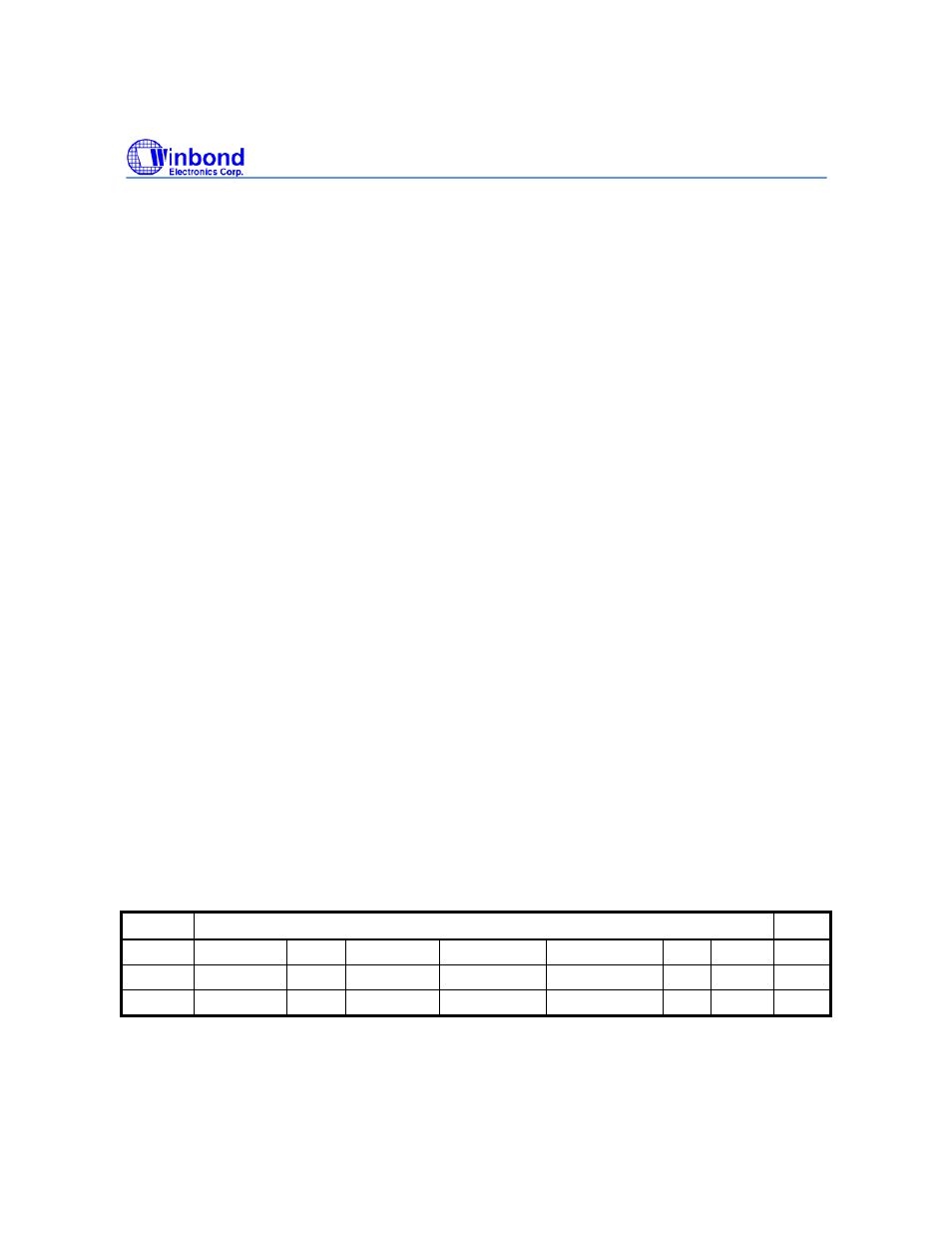

MII Management Protocol

MII Management Protocol

Access Preamble Start Operation

PHYAddr PHYRegAddr

TA DATA

IDLE

Read

1…. 1

01

10

AAAAA

RRRRR

Z0

16 bits

Z

Write

1…. 1

01

01

AAAAA

RRRRR

10

16 bits

Z