Rainbow Electronics W90N740 User Manual

Page 105

W90N740

Publication Release Date: November 26, 2004

- 101 -

Revision A4

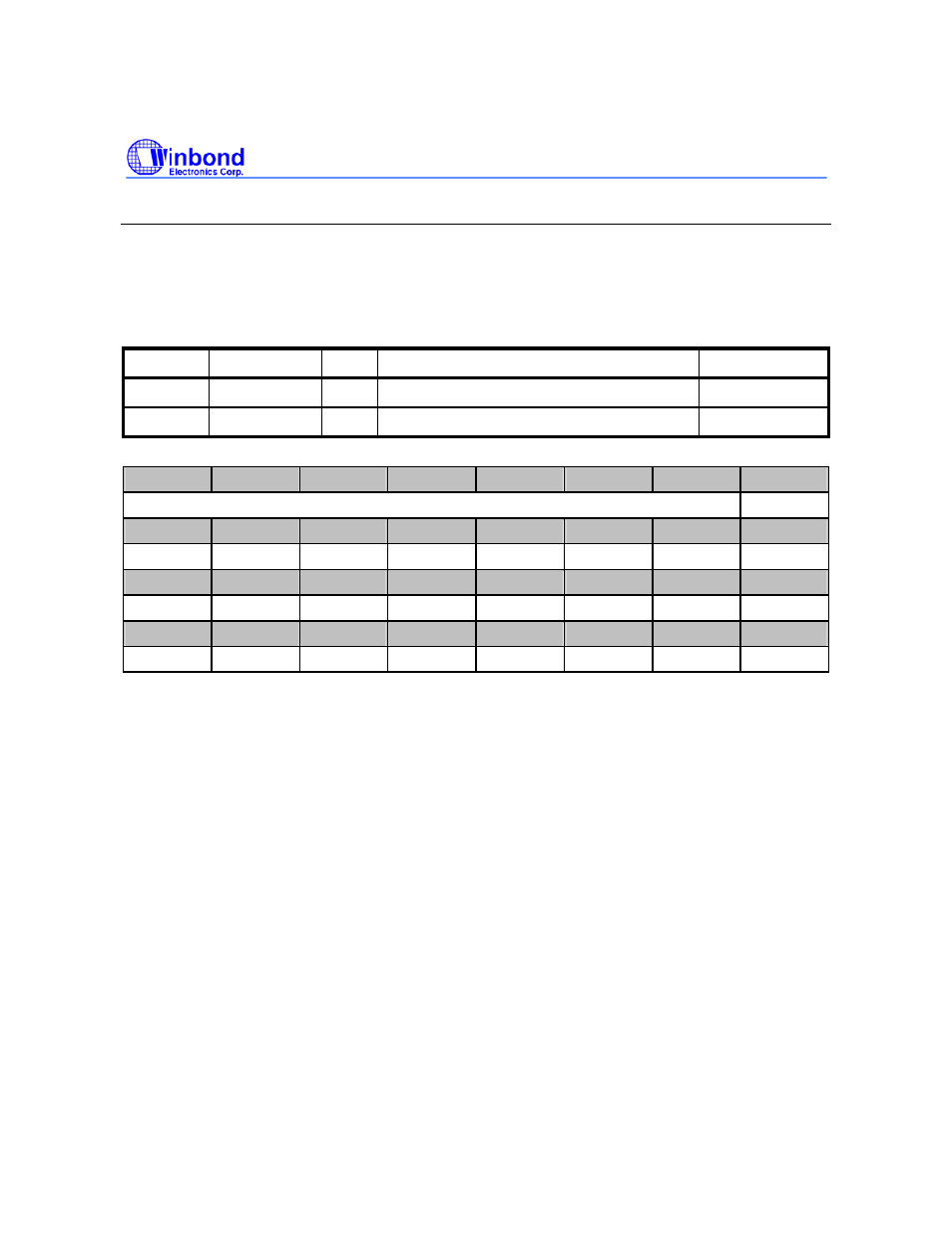

MAC Interrupt Status Register (MISTA_0, MISTA_1)

The MAC event register is used as the Ethernet event register to generate interrupts and report events

recognized by MAC controller. When an event is recognized, the MAC controller sets the

corresponding MISTA bit. Interrupts are enabled by setting, and masked by clearing, the equivalent

bits in the MAC Interrupt Enable Register (MIEN). The MISTA bits are cleared by write ones; writing

zeros has no effect.

Register Address R/W

Description

Reset

Value

MISTA_0 0xFFF0.30B4 R/W MAC

Interrupt Status Register

0x0000.0000

MISTA_1 0xFFF0.38B4 R/W MAC

Interrupt Status Register

0x0000.0000

31

30

29

28

27

26

25

24

Reserved TxBErr

23

22

21

20

19

18

17

16

TDU LC

TXABT

NCS

EXDEF

TXCP

TXEMP

TXINTR

15

14

13

12

11

10

9

8

Reserved CFR NATErr NATOK RxBErr RDU DENI DFOI

7

6

5

4

3

2

1

0

MMP RP ALIE

RXGD

PTLE

RXOV

CRCE

RXINTR

TxBErr [24]: Transmit Bus Error interrupt

Default value: 0

This field will be set if access error from EMC to memory (for example, address undefined in system) is

occurred. If the status and EnTxBErr in MIEN are both set, the EMC_TxINT will be triggered. If the

status is set, the Tx operation will be ceased and the software reset to reset the EMC is recommended.

TDU [23]: Transmit Descriptor Unavailable interrupt

Default value: 0

This field will be set if the transmit descriptors owned to the TxDMA is unavailable. If the status and

EnTDU in MIEN are both set, the EMC_TxINT will be triggered. When it is set, the TxDMA operation will

be ceased till the user issues a write command to Transmit Start Demand register to restart the Tx

operation.

LC [22]: Late Collision

Default value: 0

This bit will be set if a collision occurs after 512 bit times.