Rainbow Electronics W90N740 User Manual

Page 145

W90N740

Publication Release Date: November 26, 2004

- 141 -

Revision A4

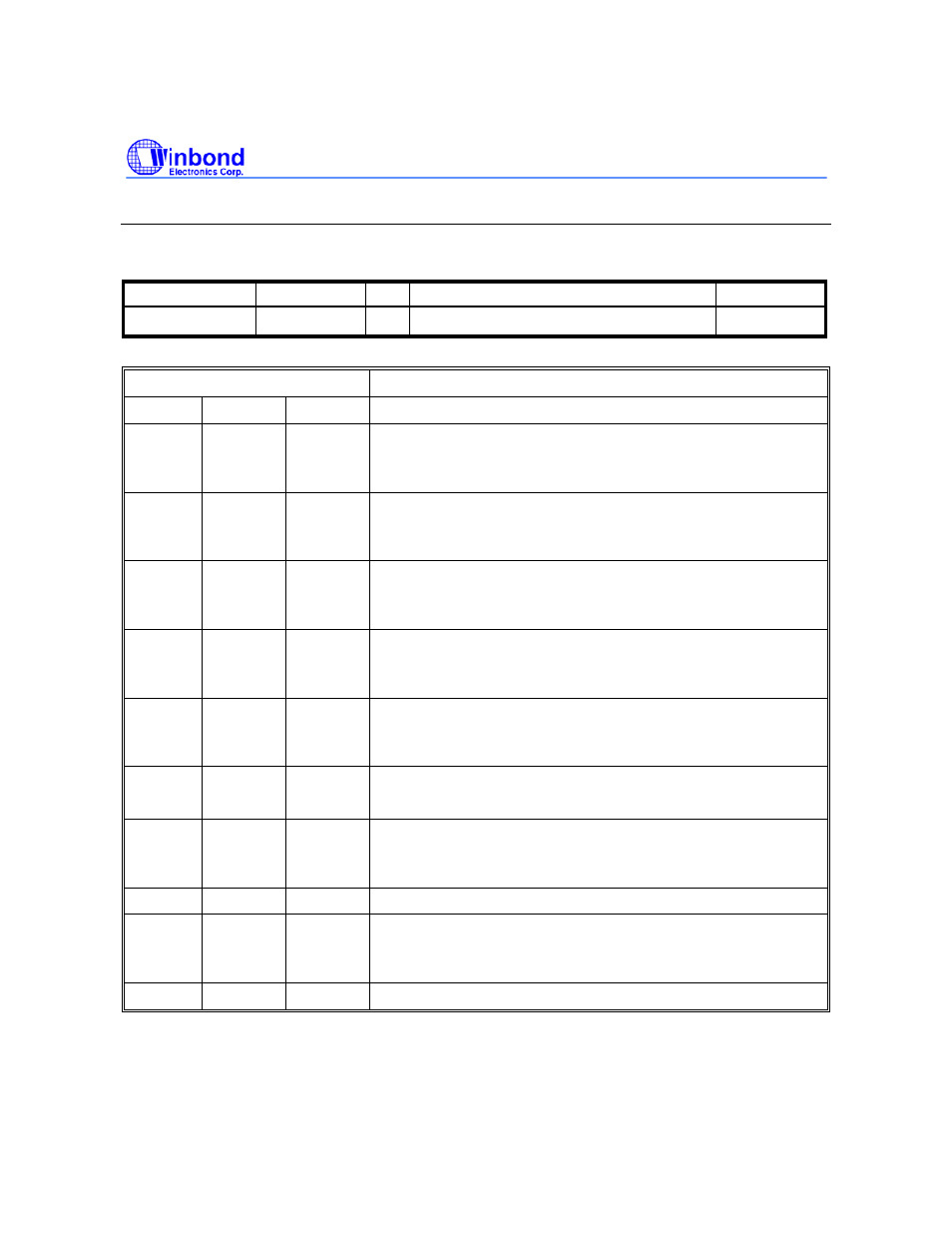

Host Controller Interrupt Status Register (HcInterruptStatus)

All bits are set by hardware and cleared by software.

Register Address

R/W

Description

Reset

Value

HcInterruptStatus 0xFFF0.500C

R/W Host Controller Interrupt Status Register

0x0000.0000

Register: HcInterruptStatus

Bits Reset R/W

Description

0 0b R/W

SchedulingOverrun

Set when the List Processor determines a Schedule Overrun has

occurred.

1 0b R/W

WritebackDoneHead

Set after the Host Controller has written HcDoneHead to

HccaDoneHead.

2 0b R/W

StartOfFrame

Set when the Frame Management block signals a ‘Start of Frame’

event.

3 0b R/W

ResumeDetected

Set when Host Controller detects resume signaling on a downstream

port.

4 0b R

UnrecoverableError

This event is not implemented and is hard-coded to ‘0.’ Writes are

ignored.

5 0b R/W

FrameNumberOverflow

Set when bit 15 of FrameNumber changes value.

6 0b R/W

RootHubStatusChange

This bit is set when the content of HcRhStatus or the content of any

HcRhPortStatus register has changed.

29-7

0h

-

Reserved. Read/Write 0's

30 0b R/W

OwnershipChange

This bit is set when the OwnershipChangeRequest bit of

HcCommandStatus is set.

31

0h

-

Reserved. Read/Write 0's